# **Freescale Semiconductor**

Data Sheet: Technical Data

Document Number: MP3H6115A

Rev 5.1, 05/2012

# High Temperature Accuracy Integrated Silicon Pressure Sensor for Measuring Absolute Pressure, On-Chip Signal Conditioned, Temperature Compensated and Calibrated

Freescale's MP3H6115A series sensor integrates on-chip, bipolar op amp circuitry and thin film resistor networks to provide a high output signal and temperature compensation. The small form factor and high reliability of on-chip integration make the Freescale pressure sensor a logical and economical choice for the system designer.

The MP3H6115A series piezoresistive transducer is a state-of-the-art, monolithic, signal conditioned, silicon pressure sensor. This sensor combines advanced micromachining techniques, thin film metallization, and bipolar semiconductor processing to provide an accurate, high level analog output signal that is proportional to applied pressure.

#### **Features**

- Improved Accuracy at High Temperature

- · Available in Super Small Outline Package

- 1.5% Maximum Error over 0° to 85°C

- · Ideally suited for Microprocessor or Microcontroller-Based Systems

- Temperature Compensated from -40° to +125°C

- Durable Thermoplastic (PPS) Surface Mount Package

# MP3H6115A Series

15 to 115 kPa (2.2 to 16.7 psi) 0.12 to 2.8 V Output

### **Application Examples**

- Aviation Altimeters

- · Industrial Controls

- Engine Control/Manifold Absolute Pressure (MAP)

- Weather Station and Weather Reporting Device Barometers

|                   | ORDERING INFORMATION                           |          |      |            |      |               |              |          |           |

|-------------------|------------------------------------------------|----------|------|------------|------|---------------|--------------|----------|-----------|

| Device Name       | Packaging                                      | Case No. |      | # of Ports |      | Pressure Type |              |          | Device    |

| Device Name       | Options                                        | Case No. | None | Single     | Dual | Gauge         | Differential | Absolute | Marking   |

| Super Small Outli | Super Small Outline Package (MP3H6115A Series) |          |      |            |      |               |              |          |           |

| MP3H6115A6U       | Rail                                           | 1317     | •    |            |      |               |              | •        | MP3H6115A |

| MP3H6115A6T1      | Tape & Reel                                    | 1317     | •    |            |      |               |              | •        | MP3H6115A |

| MP3H6115AC6U      | Rail                                           | 1317A    |      | •          |      |               |              | •        | MP3H6115A |

| MP3H6115AC6T1     | Tape & Reel                                    | 1317A    |      | •          |      |               |              | •        | MP3H6115A |

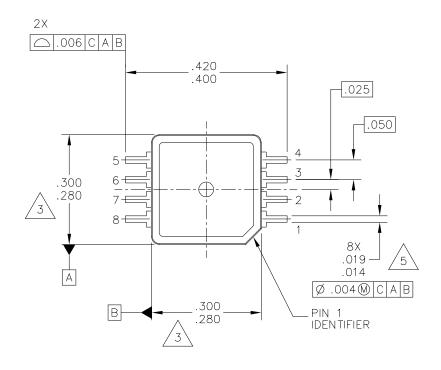

#### **SUPER SMALL OUTLINE PACKAGES**

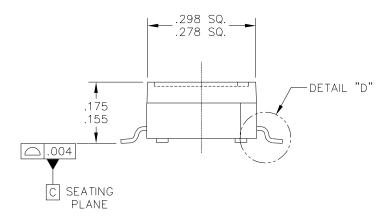

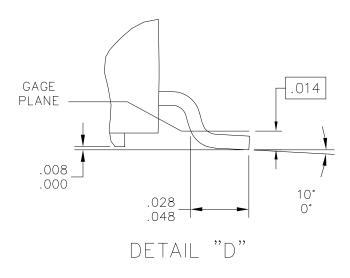

MP3H6115A6U/T1 CASE 1317-04

MP3H6115AC6U/T1 CASE 1317A-04

### **Pin Descriptions**

**Table 1. Pin Descriptions**

| Pin # | Pin Name         | Description    |

|-------|------------------|----------------|

| 1     | N/C              | Do not connect |

| 2     | V <sub>S</sub>   | Supply Voltage |

| 3     | GND              | Ground         |

| 4     | V <sub>OUT</sub> | Output Voltage |

| 5     | N/C              | Do not connect |

| 6     | N/C              | Do not connect |

| 7     | N/C              | Do not connect |

| 8     | N/C              | Do not connect |

NOTE: Pins 1, 5, 6, 7, and 8 are internal device connections. Do not connect to external circuitry or ground. Pin 1 is denoted by the chamfered corner of the package.

## **Operating Characteristics**

#### **Table 2. Operating Characteristics**

$(V_S = 3.0 \text{ Vdc}, T_A = 25^{\circ}\text{C} \text{ unless otherwise noted}, P1 > P2.)$

| Characteristic                                                      |             | Symbol           | Min   | Тур   | Max   | Unit              |

|---------------------------------------------------------------------|-------------|------------------|-------|-------|-------|-------------------|

| Pressure Range                                                      |             | P <sub>OP</sub>  | 15    | _     | 115   | kPa               |

| Supply Voltage <sup>(1)</sup>                                       |             | V <sub>S</sub>   | 2.7   | 3.0   | 3.3   | Vdc               |

| Supply Current                                                      |             | I <sub>o</sub>   | _     | 4.0   | 8.0   | mAdc              |

| Minimum Pressure Offset <sup>(2)</sup> @ V <sub>S</sub> = 3.0 Volts | (0 to 85°C) | V <sub>off</sub> | 0.079 | 0.12  | 0.161 | Vdc               |

| Full Scale Output <sup>(3)</sup> @ V <sub>S</sub> = 3.0 Volts       | (0 to 85°C) | $V_{FSO}$        | 2.780 | 2.82  | 2.861 | Vdc               |

| Full Scale Span <sup>(4)</sup> @ V <sub>S</sub> = 3.0 Volts         | (0 to 85°C) | V <sub>FSS</sub> | 2.660 | 2.70  | 2.741 | Vdc               |

| Accuracy                                                            | (0 to 85°C) | _                | _     | _     | ±1.5  | %V <sub>FSS</sub> |

| Sensitivity                                                         |             | V/P              | _     | 27    | _     | mV/kPa            |

| Response Time <sup>(5)</sup>                                        |             | t <sub>R</sub>   | _     | 1.0   | _     | ms                |

| Warm-Up Time <sup>(6)</sup>                                         |             | _                | _     | 20    | _     | ms                |

| Offset Stability <sup>(7)</sup>                                     |             | _                | _     | ±0.25 | _     | %V <sub>FSS</sub> |

- 1. Device is ratiometric within this specified excitation range.

- 2. Offset (Voff) is defined as the output voltage at the minimum rated pressure.

- 3. Full Scale Output (VFSO) is defined as the output voltage at the maximum or full rated pressure.

- 4. Full Scale Span (V<sub>FSS</sub>) is defined as the algebraic difference between the output voltage at full rated pressure and the output voltage at the minimum rated pressure.

- 5. Response Time is defined as the time for the incremental change in the output to go from 10% to 90% of its final value when subjected to a specified step change in pressure.

- 6. Warm-up Time is defined as the time required for the product to meet the specified output voltage after the pressure has been stabilized.

- 7. Offset Stability is the product's output deviation when subjected to 1000 cycles of Pulsed Pressure, Temperature Cycling with Bias Test.

# **Maximum Ratings**

Table 3. Maximum Ratings<sup>(1)</sup>

| Parametrics                                                  | Symbol           | Value         | Units |

|--------------------------------------------------------------|------------------|---------------|-------|

| Maximum Pressure (P1 > P2)                                   | P <sub>max</sub> | 400           | kPa   |

| Storage Temperature                                          | T <sub>stg</sub> | -40° to +125° | °C    |

| Operating Temperature                                        | T <sub>A</sub>   | -40° to +125° | °C    |

| Output Source Current @ Full Scale Output <sup>(2)</sup>     | l <sub>o</sub> + | 0.5           | mAdc  |

| Output Sink Current @ Minimum Pressure Offset <sup>(2)</sup> | I <sub>o</sub> - | -0.5          | mAdc  |

- 1. Exposure beyond the specified limits may cause permanent damage or degradation to the device.

- 2. Maximum Output Current is controlled by effective impedance from  $V_{out}$  to Gnd or  $V_{out}$  to  $V_S$  in the application circuit.

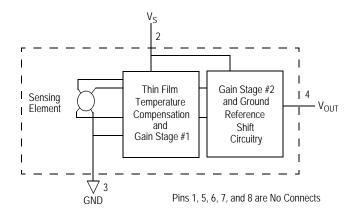

Figure 1 shows a block diagram of the internal circuitry integrated on a pressure sensor chip.

Figure 1. Fully Integrated Pressure Sensor Schematic

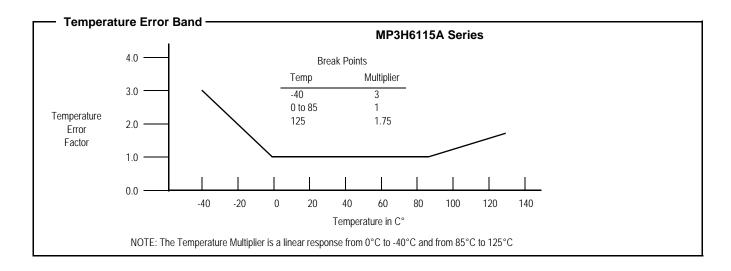

# **On-chip Temperature Compensation and Calibration**

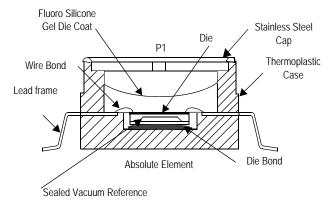

Figure 2 illustrates the absolute sensing chip in the basic Super Small Outline chip carrier (Case 1317).

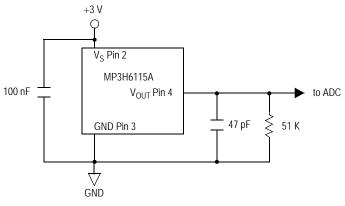

Figure 3 shows a typical application circuit (output source current operation).

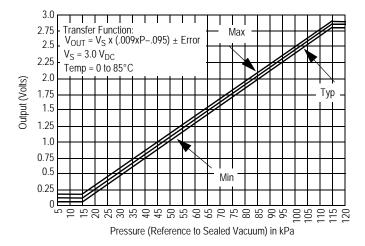

Figure 4 shows the sensor output signal relative to pressure input. Typical minimum and maximum output curves are shown for operation over 0 to 85°C temperature range. The output will saturate outside of the rated pressure range.

A fluorosilicone gel isolates the die surface and wire bonds from the environment, while allowing the pressure signal to be transmitted to the silicon diaphragm. The MP3H6115A series pressure sensor operating characteristics, internal reliability and qualification tests are based on use of dry air as the pressure media. Media other than dry air may have adverse effects on sensor performance and long-term reliability. Contact the factory for information regarding media compatibility in your application.

Figure 2. Cross Sectional Diagram SSOP (not to scale)

Figure 3. Typical Application Circuit (Output Source Current Operation)

Figure 4. Output versus Absolute Pressure

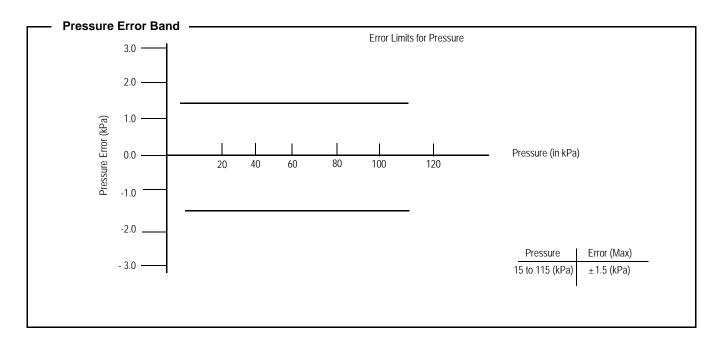

### **Transfer Function (MP3H6115A)**

Normal Transfer Value:  $V_{OUT} = V_S x (0.009 x P - 0.095)$

$\pm$  (Pressure Error x Temp. Factor x 0.009 x  $V_S$ )

$V_S = 3.0 \pm 0.3 V_{DC}$

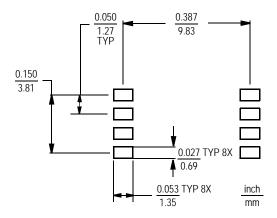

### MINIMUM RECOMMENDED FOOTPRINT FOR SMALL AND SUPER SMALL PACKAGES

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor package must be the correct size to ensure proper solder connection interface between the board and the package. With the correct pad geometry, the packages will self-align when subjected to a

solder reflow process. It is always recommended to fabricate boards with a solder mask layer to avoid bridging and/or shorting between solder pads, especially on tight tolerances and/or tight layouts.

Figure 5. SSOP Footprint (Case 1317 and 1317A)

|        | LE SEMICONDUCTOR, INC.<br>RIGHTS RESERVED. | MECHANICAL OU | TLINE   | PRINT VERSION NO   | T TO SCALE  |

|--------|--------------------------------------------|---------------|---------|--------------------|-------------|

| TITLE: | 8 IFAD                                     |               | DOCUME  | NT NO: 98ARH99066A | REV: H      |

|        | SSUB                                       |               | CASE NU | JMBER: 1317-04     | 13 APR 2012 |

|        | J J U I                                    |               | STANDAF | RD: NON-JEDEC      |             |

PAGE 1 OF 3

### CASE 1317-04 ISSUE H SUPER SMALL OUTLINE PACKAGE

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. |        | MECHANICAL OUTLINE |         | PRINT VERSION NOT TO SCALE |             |

|------------------------------------------------------|--------|--------------------|---------|----------------------------|-------------|

| TITLE:                                               | 8 IFAD |                    | DOCUME  | NT NO: 98ARH99066A         | REV: H      |

|                                                      | SSAP   |                    | CASE NU | JMBER: 1317-04             | 13 APR 2012 |

|                                                      | 3301   |                    | STANDAF | RD: NON-JEDEC              |             |

PAGE 2 OF 3

### CASE 1317-04 ISSUE H SUPER SMALL OUTLINE PACKAGE

### NOTES:

- 1. ALL DIMENSIONS IN INCHES.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSION SHALL NOT EXCEED .006 INCHES PER SIDE.

4. ALL VERTICAL SURFACES TO BE 5' MAXIMUM.

<u>/</u>5.\

\ DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION.

ALLOWABLE DAMBAR PROTRUSION SHALL BE .008 INCHES MAXIMUM.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE | JTLINE PRINT VERSION NOT TO SCALE |             |  |

|------------------------------------------------------|--------------------|-----------------------------------|-------------|--|

| TITLE: 8 IFAD                                        | DOCUME             | DOCUMENT NO: 98ARH99066A REV: H   |             |  |

| O LLAD                                               | CASE N             | UMBER: 1317-04                    | 13 APR 2012 |  |

| 33UP                                                 | STANDA             | RD: NON-JEDEC                     |             |  |

PAGE 3 OF 3

### CASE 1317-04 ISSUE H SUPER SMALL OUTLINE PACKAGE

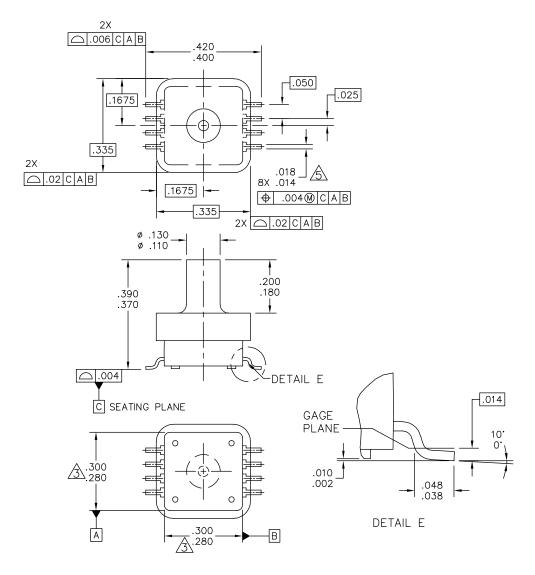

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO  | ): 98ARH99089A   | REV: D      |

| 8 LD, PORTED S                                       | SOP       | CASE NUMBER  | R: 1317A-04      | 26 OCT 2006 |

|                                                      |           | STANDARD: NO | N-JEDEC          |             |

PAGE 1 OF 2

### CASE 1317A-04 ISSUE D SUPER SMALL OUTLINE PACKAGE

#### NOTES:

- 1. ALL DIMENSIONS IN INCHES.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSION SHALL NOT EXCEED .006 INCHES PER SIDE.

4. ALL VERTICAL SURFACES TO BE 5' MAXIMUM.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION.

ALLOWABLE DAMBAR PROTRUSION SHALL BE .008 INCHES MAXIMUM.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|--------------------|------------------|-------------|

| TITLE:                                               | DOCUMENT N         | 0: 98ARH99089A   | REV: D      |

| 8 LD, PORTED SS                                      | OP CASE NUMBE      | R: 1317A-04      | 26 OCT 2006 |

|                                                      | STANDARD: N        | ON-JEDEC         |             |

PAGE 2 OF 2

### **CASE 1317A-04 ISSUE D SUPER SMALL OUTLINE PACKAGE**

# Pressure

### **Table 4. Revision History**

| Revision number | Revision date | Description of changes                                             |

|-----------------|---------------|--------------------------------------------------------------------|

| 5.1             | 05/2012       | Updated Package Drawing 98ARH99066A was Rev. F, updated to Rev. H. |

#### How to Reach Us:

Home Page: www.freescale.com

Web Support:

http://www.freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: http://www.reg.net/v2/webservices/Freescale/Docs/TermsandConditions.htm.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off.

All other product or service names are the property of their respective owners.

© 2012 Freescale Semiconductor, Inc. All rights reserved.