# V<sub>DDQ</sub> and V<sub>TT</sub> Termination Regulation for DDR DRAM Memory Power Utilizing the ISL6530

Application Note April 2002 AN9993

Author: Douglas Mattingly

#### Introduction

The ISL6530 and the ISL6531 are dual, voltage mode controllers with many functions that are needed for DDR DRAM Memory power applications. The ISL6530 and ISL6531 contain high performance error amplifiers, a high accuracy reference, an internal 50% tracking reference, a fixed 300kHz internal oscillator with a 90° phase shift for dual synchronous buck regulators, over-current protection circuitry, Power Good indication, and two shut down options. There are two MOSFET drivers for use in both synchronous-rectified Buck converters. The ISL6530 and ISL6531 are also capable of regulating the output voltage while the tracking DC-DC converter is sinking current. All these features are packaged in a 24 lead SOIC or a small 32 Lead 4x4[mm] MLFP.

#### ISL6530 and ISL6531

The ISL6530 and ISL6531 are pin for compatible replacements to each other. All functions are identical between the two ICs. The difference between the ISL6530 and the ISL6531 lies in the compensation of the  $V_{TT}$  regulator. The ISL6531 features internal compensation for the  $V_{TT}$  regulator. More complete descriptions of both ICs can be found in their respective datasheets[1,2].

# Reference Designs

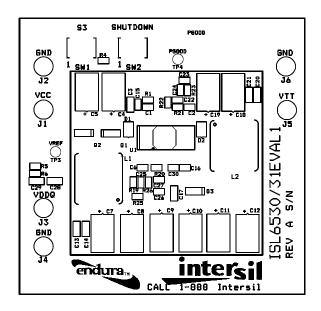

There are four different evaluation boards that are included in the scope of this application note. Table 1 describes each of the boards.

Table 1 - Evaluation Boards

| Board Name   | IC        | Package        |

|--------------|-----------|----------------|

| ISL6530EVAL1 | ISL6530CB | 24 ld SOIC     |

| ISL6530EVAL2 | ISL6530CR | 32 ld 4x4 MLFP |

| ISL6531EVAL1 | ISL6531CB | 24 ld SOIC     |

| ISL6531EVAL2 | ISL6531CR | 32 ld 4x4 MLFP |

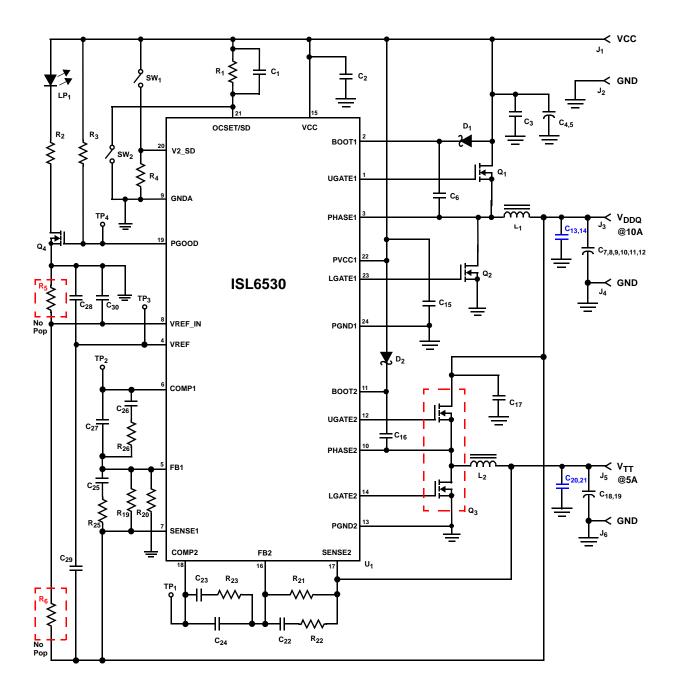

The ISL6530EVAL1 is an evaluation board that highlights the operation of the ISL6530 in an embedded DDR DRAM Memory Power application. The  $V_{DDQ}$  supply has been designed to supply 2.5V at a maximum load of 10A. The  $V_{TT}$  termination supply will track the  $V_{DDQ}$  supply at 50% and was designed for a maximum load of 5A, sourcing or sinking. The schematic, Bill of Materials, and Board Layout for the ISL6530EVAL1 can be found in the Appendix. Customization of the reference design is discussed in this application note.

#### **Quick Start Evaluation**

The ISL6530/31EVAL1 board is shipped 'ready to use' right from the box. The ISL6530/31EVAL1 board will only accept 5V from a standard power supply. Both outputs can be exercised through external loads. The  $V_{TT}$  regulator has the ability to source or sink current while the  $V_{DDQ}$  regulator may only source current.

There are posts available on the board for introducing power to the board and also for drawing current from the regulated outputs. Two probe points are also available for use. These probe points provide Kelvin connections to the PGOOD (TP4) and VREF\_OUT (TP3) pins.

An LED lights up to indicate that the output voltages are within regulation.

# Recommended Test Equipment

To test the functionality of the ISL6530, the following equipment is recommended:

- A 5V, 10A capable bench power supply

- Two electronic loads

- Four channel oscilloscope with probes

- Precision digital multimeters

#### Power and Load Connections

There are 3 sets of jumpers that are used for the supplying the input voltage and loading the  $V_{\mbox{\scriptsize DDQ}}$  and  $V_{\mbox{\scriptsize TT}}$  outputs.

#### **INPUT VOLTAGE**

Connect the positive lead of the 5V bench power supply to the VCC post (J1). Connect the ground lead of the supply to GND post (J2).

#### LOADING V<sub>DDQ</sub>

Connect the positive terminal of the first electronic load to the VDDQ post (J3). Connect the return terminal of the same load to the GND post (J4).

## LOADING V<sub>TT</sub> - SOURCING CURRENT

To test  $V_{TT}$  while the regulator sources current, connect the positive terminal of the second electronic load to the VTT post (J5). Connect the return terminal of the same load to the GND post (J6).

## LOADING V<sub>TT</sub> - SINKING CURRENT

To test  $V_{TT}$  while the regulator sinks current, connect the positive terminal of the second electronic load to the VDDQ post (J3). Connect the return terminal of the same load to the VTT post (J5).

CAUTION: The return terminal of the load must float for this to work properly.

# Start Up

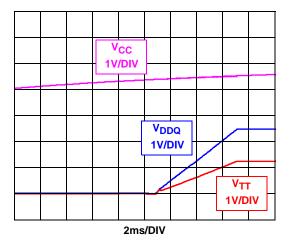

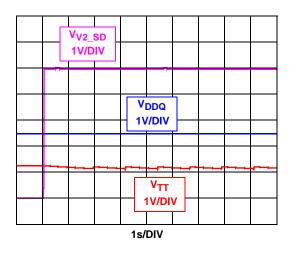

There are two distinct start up methods for the  $V_{DDQ}$  and  $V_{TT}$  regulators. The first method is invoked through the application of power to the IC. The Softstart feature allows for a controlled turn on of the outputs once the Power On Reset (POR) threshold of the input voltage has been reached. Figure 1 shows the start up profile of the two regulators in relation to the start up of the 5V input supply.

FIGURE 1. START UP FROM POR

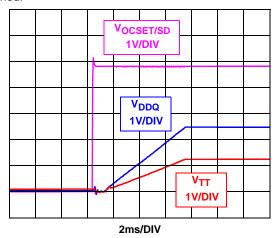

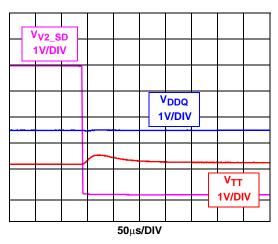

The second method of start up is through the use of the Shutdown feature. Holding the OCSET/SD pin below 0.8V will disable both regulators by forcing both the upper and lower MOSFETs of both regulators off. Releasing the OCSET/SD pin allow the regulators to start up. Figure 2 show the start up profile of the two regulators with this method.

FIGURE 2. START UP FROM SHUT DOWN

## Shutdown

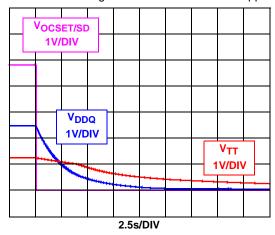

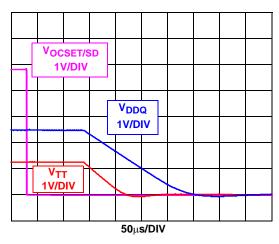

Shutting Down Both  $V_{\mbox{\scriptsize DDQ}}$  and  $V_{\mbox{\scriptsize TT}}$

As discussed in the previous section, if the OCSET/SD pin is pulled down and held below 0.8V, both the  $\rm V_{DDQ}$  and  $\rm V_{TT}$  regulators will be turned off. Figure 3 shows the shutdown

profile of the regulators with no load applied. Figure 4 shows the shutdown of the regulators will their full loads applied.

FIGURE 3. SHUTDOWN WITH NO LOAD

FIGURE 4. SHUTDOWN WITH FULL LOAD

V<sub>TT</sub> Sleep State

The V $_{TT}$  regulator can be placed in a sleep state where the output is regulated to a wider tolerance while V $_{DDQ}$  continues to regulate. This is done by applying a logic high signal to the V2\_SD pin. During this state, V $_{DDQ}$  can support a load while V $_{TT}$  cannot. This allows a very quick recovery back into synchronous buck mode. Once removed from this state by releasing the high signal on the V2\_SD pin, the output rapidly returns to regulation. Figure 5 illustrates the VTT regulator going into sleep mode and Figure 6 shows the regulator being taken out of the sleep state.

## Reference Design Customization

The ISL6530/31EVAL1 board has a number of options that will allow the designer to customize the board. One modification that can be made is to overdrive the internal resistor divider which sets the reference voltage for the  $V_{TT}$  regulator in relation to  $V_{DDQ}$ . This may be done by populating resistors R5 and R6, as to create a tracking ratio

FIGURE 5. V<sub>TT</sub> SLEEP MODE

FIGURE 6. V<sub>TT</sub> RETURN FROM SLEEP MODE

other than the internally generated 50%. Please refer to the datasheet for proper component selection.

In order to increase performance during a load transient on either output, two 0603 capacitor pads have been provided at each output. These pads allow the designer to add ceramic capacitors on the output. Ceramic capacitors help to decrease the overall output capacitance ESR while they have much lower lead inductance. The pad reference designators are C20 and C21 for the  $V_{\mbox{\scriptsize TT}}$  output and reference designators C13 and C14 for the  $V_{\mbox{\scriptsize DDQ}}$  output.

The VDDQ output also has two extra bulk capacitor pads, designated C11 and C12. The designer may wish to utilize these to decrease the ripple voltage, improve transient performance or both.

# Ripple Voltage

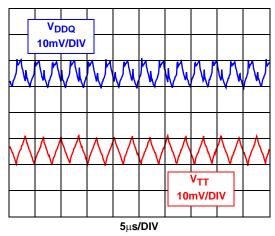

Figure 7 shows the ripple voltage on both the  $V_{\mbox{\scriptsize DDQ}}$  output and the  $V_{\mbox{\scriptsize TT}}$  output.

## **Transient Performance**

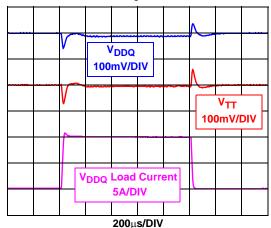

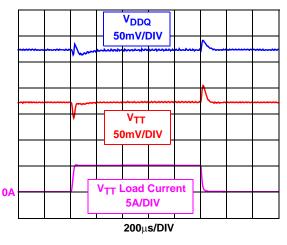

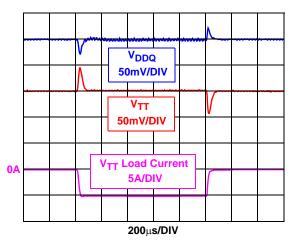

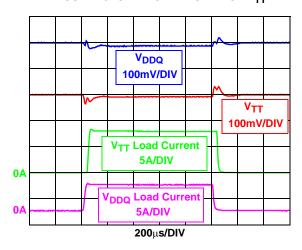

Figures 8, 9, 10 and 11 show the response of the outputs when subjected to a variety of transient loads. Figure 8

FIGURE 7. V<sub>DDQ</sub> AND V<sub>TT</sub> RIPPLE VOLTAGES

shows V<sub>DDQ</sub> under transient loading. Figure 9 shows V<sub>TT</sub> under a transient loading that causes V<sub>TT</sub> to source current. Figure 10 shows V<sub>TT</sub> under a transient that causes V<sub>TT</sub> to sink current. Figure 11 shows both V<sub>DDQ</sub> and V<sub>TT</sub> under simultaneous transient loading.

FIGURE 8. TRANSIENT ON VDDQ

FIGURE 9. SOURCING TRANSIENT ON V<sub>TT</sub>

FIGURE 10. SINKING TRANSIENT ON V<sub>TT</sub>

FIGURE 11. TRANSIENTS ON  $V_{\text{DDQ}}$  AND  $V_{\text{TT}}$

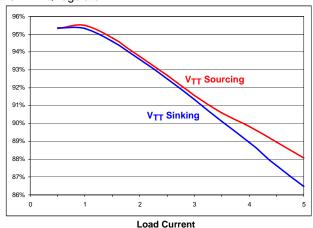

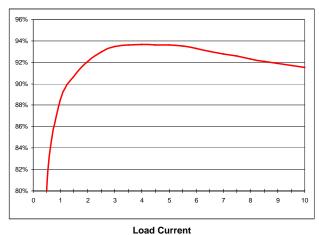

# **Efficiency**

Each channel of the ISL6530 is highly efficient which leads to a high overall system efficiency. The efficiency of the  $V_{TT}$  regulator in current sourcing and current sinking modes is shown in Figures 12. Figure 13 illustrates the efficiency of the VDDQ regulator.

FIGURE 12. V<sub>TT</sub> EFFICIENCY (SOURCING CURRENT)

FIGURE 13. V<sub>DDQ</sub> EFFICIENCY

## Conclusion

The ISL6530/31EVAL1 board is a dual DC-DC converter reference design for DDR Memory Power applications that require up to 10A on  $V_{DDQ}$  and up to 5A on  $V_{TT}$ . In addition, the design may be modified for applications with different requirements.

## References

For Intersil documents available on the web, see http://www.intersil.com/

[1] ISL6530 Data Sheet, Intersil Corporation, FN9052

[2] ISL6531 Data Sheet, Intersil Corporation, FN9053

# ISL6530EVAL1 Schematic

# ISL6530EVAL1 Bill of Material

| Ref Des                 | Description                                               | Vendor    | Vendor P/N   | Qty |

|-------------------------|-----------------------------------------------------------|-----------|--------------|-----|

| C1                      | 1nF Capacitor, 0603                                       | Various   |              | 1   |

| C2,6,15,16              | 0.1μF Capacitor, 0603                                     | Various   |              | 4   |

| C3,17                   | 1μF Capacitor, 0805                                       | Various   |              | 3   |

| C4,5,7,8,9,<br>10,18,19 | 150μF Capacitor                                           | Panasonic | EEFUE0J151R  | 8   |

| C11,12                  | Not Populated (Reserved for 150μF Panasonic SP Capacitor) |           |              |     |

| C22                     | 10nF Capacitor, 0603                                      | Various   |              | 1   |

| C24                     | 68pF Capacitor, 0603                                      | Various   |              | 1   |

| C23                     | 2700pF Capacitor, 0603                                    | Various   |              | 1   |

| C25                     | 15nF Capacitor, 0603                                      | Various   |              | 1   |

| C27                     | 100pF Capacitor, 0603                                     | Various   |              | 1   |

| C26                     | 5600pF Capacitor, 0603                                    | Various   |              | 1   |

| C28,29                  | 0.1μF Capacitor, 0805                                     | Various   |              | 2   |

| C13,14,20,<br>21        | 0805 Capacitor (Not Populated)                            |           |              | 0   |

| D1,2                    | Diode, 30mA, 30V                                          | Digikey   | MA732        | 2   |

| L1, L2                  | 1μH Inductor                                              | Panasonic | ETQP6F1R0SFA | 2   |

| Q1,2                    | MOSFET, 8 Pin SOIC                                        | Fairchild | ITF86130     | 2   |

| Q3                      | Dual MOSFET, 8 Pin SOIC                                   | Fairchild | ITF86110     | 1   |

| Q4                      | 2N7002 MOSFET, SOT23                                      | Various   |              | 1   |

| R1                      | 3.48kΩ 1% Resistor, 0603                                  | Various   |              | 1   |

| R2                      | 750Ω 1% Resistor, 0603                                    | Various   |              | 1   |

| R3,4                    | 10kΩ 1% Resistor, 0603                                    | Various   |              | 2   |

| R5,6                    | 0603 Resistor (Not Populated)                             |           |              | 0   |

| R19,21                  | 3.01kΩ 1% Resistor, 0603                                  | Various   |              | 1   |

| R22                     | 158Ω 1% Resistor, 0603                                    | Various   |              | 1   |

| R23                     | 8.87kΩ 1% Resistor, 0603                                  | Various   |              | 1   |

| R20                     | 1.43kΩ 1% Resistor, 0603                                  | Various   |              | 1   |

| R26                     | 6.34kΩ 1% Resistor, 0603                                  | Various   |              | 1   |

| R25                     | 100Ω 1% Resistor, 0603                                    | Various   |              | 1   |

| SW1,2                   | Pushbutton, miniature                                     | Digikey   | CKN1100-ND   | 2   |

| Ref Des          | Description                                               | Vendor   | Vendor P/N  | Qty |

|------------------|-----------------------------------------------------------|----------|-------------|-----|

| LP1              | LED                                                       | Digikey  | L63111CT-ND | 1   |

| U1               | Dual Synchronous Buck PWM Controller for DDR Applications | Intersil | ISL6530CB   | 1   |

| TP3,4            | Test Points                                               | Digikey  | 5002K-ND    | 2   |

| J1,2,3,4,<br>5,6 | Test Points                                               | Keystone | 1514-2      | 6   |

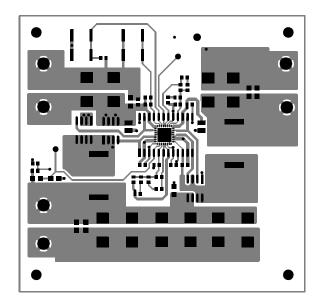

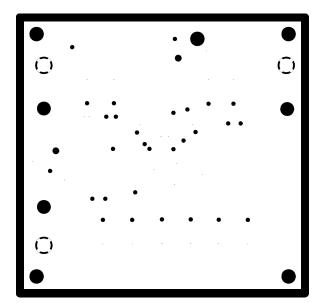

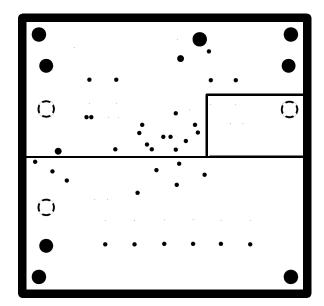

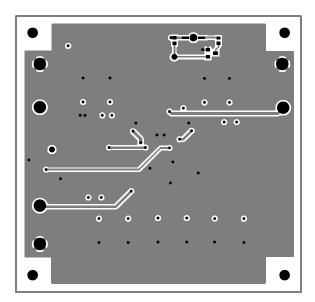

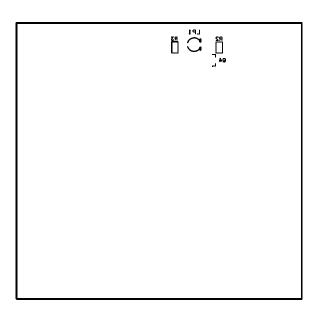

# ISL6530EVAL1 Layout

# TOP SILK SCREEN

TOP

# INTERNAL 1 GROUND

# INTERNAL 2 POWER

## **BOTTOM**

# **BOTTOM SILK SCREEN**

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

## Sales Office Headquarters

## **NORTH AMERICA**

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618 TEL: (949) 341-7000

FAX: (949) 341-7123

Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946

#### **EUROPE**

Intersil Europe Sarl Ave. William Graisse, 3 1006 Lausanne Switzerland

TEL: +41 21 6140560 FAX: +41 21 6140579

## **ASIA**

Intersil Corporation Unit 1804 18/F Guangdong Water Building 83 Austin Road

TST, Kowloon Hong Kong TEL: +852 2723 6339 FAX: +852 2730 1433