## IFX80471

Step-Down DC/DC Controller

IFX80471SKV IFX80471SKV50

## **Data Sheet**

Rev. 1.0, 2011-02-07

## Standard Power

### **Table of Contents**

### **Table of Contents**

| I          | Overview                                                   | . 3 |

|------------|------------------------------------------------------------|-----|

| 2          | Block Diagram                                              | . 4 |

| 3          | Pin Configuration                                          | . 5 |

| 3.1        | Pin Assignment                                             | . 5 |

| 3.2        | Pin Definitions and Functions                              | . 5 |

| 1          | General Product Characteristics                            | . 7 |

| 1.1        | Absolute Maximum Ratings                                   |     |

| 1.2        | Functional Range                                           |     |

| 1.3        | Thermal Resistance                                         |     |

|            | Electrical Characteristics                                 | 10  |

| 5.1        | Electrical Characteristics                                 |     |

| 5.2        | Typical Performance Characteristics                        |     |

|            |                                                            |     |

| )<br>` 4   | Detailed Circuit Description                               |     |

| 6.1<br>6.2 | PFM/PWM Step-down regulator                                |     |

| 5.2<br>5.3 | Battery voltage sense                                      |     |

| ).3        | · ·                                                        |     |

| 7          | Application Information                                    |     |

| 7.1        | General                                                    |     |

| 7.2        | Output voltage at adjustable version - feedback divider    |     |

| 7.3        | SI_Enable                                                  |     |

| 7.3.1      | Battery sense comparator - voltage divider                 |     |

| 7.4<br>7.5 | Undervoltage reset - delay time                            |     |

| 7.5        | 100% duty-cycle operation and dropout                      |     |

| 7.6<br>7.7 | SYNC Input and Frequency Control                           |     |

| 7.8        | Buck converter circuit                                     |     |

| 7.8.1      | Buck inductance (L1) selection in terms of ripple current: |     |

| 7.8.2      | Determining the current limit                              |     |

| 7.8.3      | PFM and PWM thresholds                                     |     |

| 7.8.4      | Buck output capacitor (COUT) selection:                    |     |

| 7.8.5      | Input capacitor (CIN1) selection:                          |     |

| 7.8.6      | Freewheeling diode / catch diode (D1)                      |     |

| 7.8.7      | Buck driver supply capacitor (CBDS)                        |     |

| 7.8.8      | Input pi-filter components for reduced EME                 |     |

| 7.8.9      | Frequency compensation                                     | 25  |

| 7.9        | Components recommendation - Overview                       | 26  |

| 7.10       | Layout recommendation                                      | 26  |

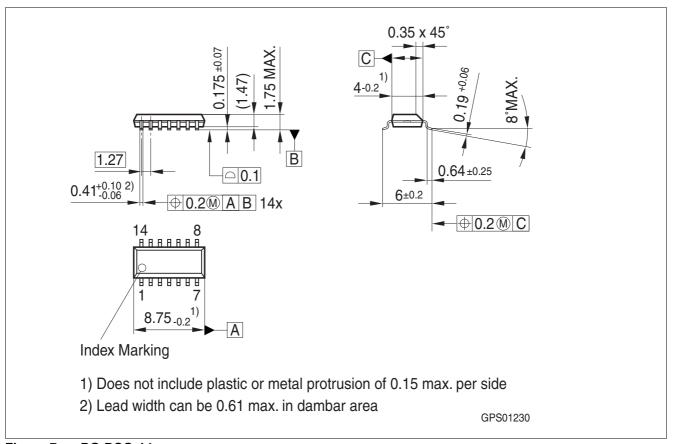

| 3          | Package Outlines                                           | 28  |

| 9          | Revision History                                           | 29  |

### Step-Down DC/DC Controller

IFX80471

### 1 Overview

#### **Features**

- Input voltage range from 5V up to 60V

- Output voltage: 5V fixed or adjustable

- Output voltage accuracy: 3%

- Output current up to 2.3A

- 100% maximum duty cycle

- Less than 120µA quiescent current at low loads<sup>1)</sup>

- 2µA max. shutdown current at device off (IFX80471SKV)

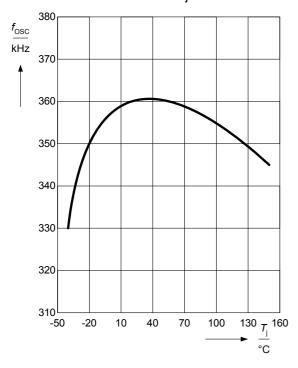

- Fixed 360kHz switching frequency

- · Frequency synchronization input for external clocks

- Current Mode control scheme

- Integrated output undervoltage reset circuit<sup>2)</sup>

- On chip low battery detector (on chip comparator)

- Temperature range -40°C to 125 °C

- Green Product (RoHS compliant)

- 1) dependent on external component

PG-DSO-14

For automotive and transportation applications, please refer to the Infineon TLE and TLF voltage regulator series.

#### **Description**

The IFX80471 step-down DC-DC switching controllers provide high efficiency over loads ranging from 1mA up to 2.3A. A unique PWM/PFM control scheme operates with a duty cycle up to 100% resulting in a very low dropout voltage. This control scheme eliminates minimum load requirements and reduces the supply current under light loads to 120μA, depending on dimensioning of external components. In addition the adjustable version IFX80471SKV can be shut down via the Enable input reducing the input current to <2μA. The IFX80471 step-down controllers drive an external P-channel MOSFET, allowing design flexibility for applications up to 11.5W of output power at 5V output voltage. The IFX80471 offers high switching frequency of up to 360kHz as well as operation in continuous-conduction mode and allows the usage of tiny surface-mount inductors. Output capacitor requirements are also reduced, minimizing PC board area and system costs. The output voltage of the IFX80471SKV50 is preset to 5V and is adjustable for the IFX80471SKV. The IFX80471SKV50 features a reset function with a threshold between 4.5V and 4.8V, including a small hysteresis of typ. 50mV. Input voltages of both IFX80471 versions can be up to 60V.

| Туре          | Package   | Marking   |

|---------------|-----------|-----------|

| IFX80471SKV   | PG-DSO-14 | I80471V   |

| IFX80471SKV50 | PG-DSO-14 | I80471V50 |

Data Sheet 3 Rev. 1.0, 2011-02-07

<sup>&</sup>lt;sup>2)</sup> for the adjustable version IFX80471SKV the reset functionality is available for output voltages > 7V

**Block Diagram**

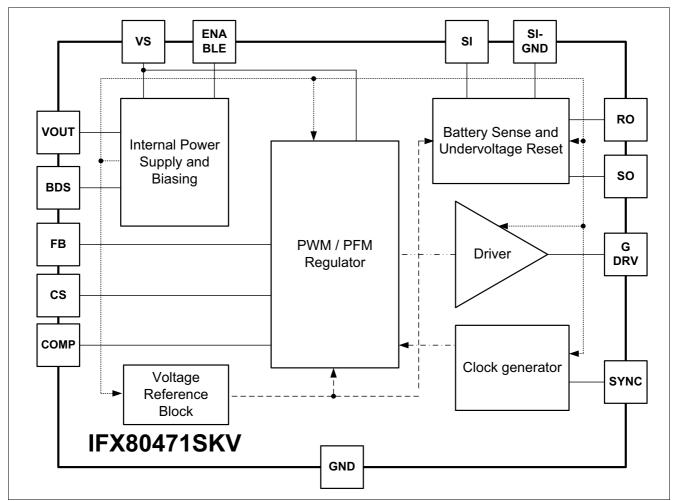

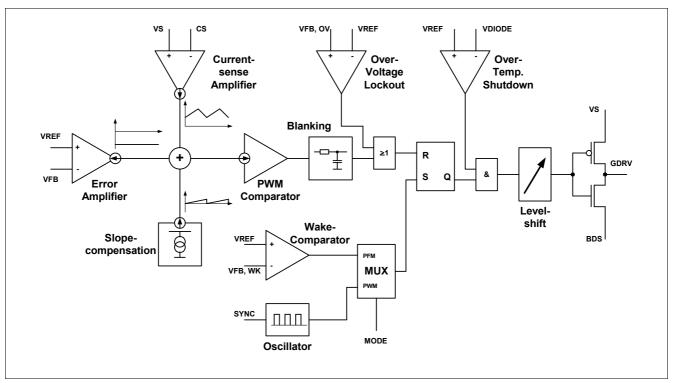

### 2 Block Diagram

Figure 1 Block Diagram

**Pin Configuration**

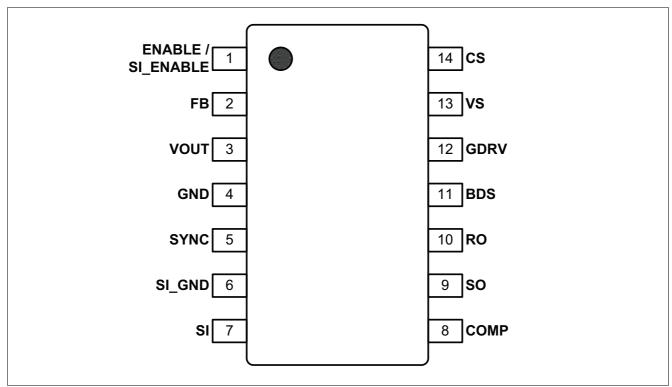

## 3 Pin Configuration

### 3.1 Pin Assignment

Figure 2 Pin Configuration

### 3.2 Pin Definitions and Functions

| Pin | Symbol    | Function                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ENABLE    | Active-High enable input (only adjustable version, IFX80471SKV) for the device.  The device is shut down when ENABLE is driven low. In this shut down-mode the reference, the output and the external MOSFET are turned off. Connect to logic high for normal operation.                                                                                 |

| 1   | SI_ENABLE | Active-High enable input (only 5V version, IFX80471SKV50) for SI_GND input. SI_GND is switched to high impedance when SI_ENABLE is low. High level at SI_ENABLE connects SI_GND to GND with low impedance. SO is undefined when SI_ENABLE is low.                                                                                                        |

| 2   | FB        | Feedback input.  1. For adjustable version (IFX80471SKV) connect this pin to an external voltage divider from the output to GND (see Chapter 7.2).  2. For the 5V fixed output voltage version (IFX80471SKV50) the FB is connected to an on-chip voltage divider supplied internally by VOUT. It does not have to be connected externally to the output. |

| 3   | VOUT      | Buck output voltage input.  Input for the internal supply. Connect always to the output of the buck converter (output capacitor).                                                                                                                                                                                                                        |

### **Pin Configuration**

| Pin | Symbol | Function                                                                                                                                                                                                                                       |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | GND    | Ground connection. Analog signal ground.                                                                                                                                                                                                       |

| 5   | SYNC   | Input for external frequency synchronization.  An external clock signal connected to this pin allows switching frequency synchronization of the device. The internal oscillator is clocked then by the frequency applied at the SYNC input.    |

| 6   | SI_GND | SI-Ground input.  Ground connection for SI comparator resistor divider. Depending on SI_ENABLE this input is switched to high impedance or low ohmic to GND.                                                                                   |

| 7   | SI     | Sense comparator input.  Input of the low-battery comparator. This input is compared to an internal 1.25V reference where SO gives the result of the comparison. Can be used for any comparison, not necessarily as battery sense.             |

| 8   | COMP   | Compensation input. Connect via RC-compensation network to GND.                                                                                                                                                                                |

| 9   | SO     | Sense comparator output. Open drain output from SI comparator at the adjustable version (IFX80471SKV), Pull down structure with an internal $20k\Omega$ pull up resistor to VOUT at the 5V version (IFX80471SKV50).                            |

| 10  | RO     | Reset output.  Open drain output from undervoltage reset comparator at the adjustable version (IFX80471SKV),  Pull down structure with an internal $20k\Omega$ pull up resistor to VOUT at the 5V version (IFX80471SKV50).                     |

| 11  | BDS    | Buck driver supply input.  Connect a ceramic capacitor between BDS and VS to generate clamped gate-source voltage to supply the driver of the PMOS power stage.                                                                                |

| 12  | GDRV   | Gate drive output.  Connect to the gate of the external P-Channel MOSFET. The voltage at GDRV swings between the levels of VS and BDS.                                                                                                         |

| 13  | VS     | Device supply input.  Connect a 220nF ceramic cap close to the pin in addition to the low ESR tantalum input capacitance.                                                                                                                      |

| 14  | CS     | Current-sense input.  Connect current-sense resistor between VS and CS. The voltage drop over the sense-resistor determines the peak current flowing in the buck circuit. The external MOSFET is turned off when the peak current is exceeded. |

### 4 General Product Characteristics

### 4.1 Absolute Maximum Ratings

### Absolute Maximum Ratings 1)

all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.      | Parameter            | Symbol                 | Limi  | t Values | Unit     | Conditions                                                                                                                                                                                    |

|-----------|----------------------|------------------------|-------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                      |                        | Min.  | Max.     |          |                                                                                                                                                                                               |

| Device su | ipply input VS       | 1                      | 1     |          | - 1      |                                                                                                                                                                                               |

| 4.1.1     | Voltage              | $V_{\sf VS}$           | -0.3  | 61       | V        | _                                                                                                                                                                                             |

| 4.1.2     | Current              | $I_{\sf VS}$           | _     | _        | _        | _                                                                                                                                                                                             |

| Current   | sense input CS       | 1                      | 1     |          | - 1      |                                                                                                                                                                                               |

| 4.1.3     | Voltage              | $V_{CS}$               | -0.3  | 61       | V        | $ V_{VS} - V_{CS}  < 0.3V$                                                                                                                                                                    |

| 4.1.4     | Current              | $I_{CS}$               | _     | _        | _        | _                                                                                                                                                                                             |

| Gate driv | ve output GDRV       | 1                      |       | -        | <b>"</b> |                                                                                                                                                                                               |

| 4.1.5     | Voltage              | $V_{GDRV}$             | - 0.3 | 61       | V        | $ \begin{array}{l} -0.3 \mathrm{V} <  V_{\mathrm{VS}} - V_{\mathrm{GDRV}}  \\ < 6.8 \mathrm{V}; \\ -0.3 \mathrm{V} <  V_{\mathrm{BDS}} - V_{\mathrm{GDRV}}  \\ < 6.8 \mathrm{V} \end{array} $ |

| 4.1.6     | Current              | $I_{GDRV}$             | _     | _        | _        | limited internally                                                                                                                                                                            |

| Buck dri  | ver supply input BDS | 1 -                    |       |          |          |                                                                                                                                                                                               |

| 4.1.7     | Voltage              | $V_{BDS}$              | - 0.3 | 61       | V        | -0.3V <  V <sub>VS</sub> - V <sub>BDS</sub>  <br>< 6.8V                                                                                                                                       |

| 4.1.8     | Current              | $I_{BDS}$              | _     | _        | _        | _                                                                                                                                                                                             |

| Feedbac   | k input FB           |                        |       | <u>'</u> | •        |                                                                                                                                                                                               |

| 4.1.9     | Voltage              | $V_{FB}$               | - 0.3 | 6.8      | V        | _                                                                                                                                                                                             |

| 4.1.10    | Current              | $I_{FB}$               | _     | _        | _        | _                                                                                                                                                                                             |

| Enable i  | nput SI_ENABLE       |                        |       |          |          |                                                                                                                                                                                               |

| 4.1.11    | Voltage              | $V_{ m SI\_ENABLE}$    | - 0.3 | 61       | V        | IFX80471SKV50                                                                                                                                                                                 |

| 4.1.12    | Current              | $I_{\rm SI\_ENABLE}$   | _     | _        | -        | -                                                                                                                                                                                             |

| SI-Grou   | nd input SI_GND      |                        |       |          |          |                                                                                                                                                                                               |

| 4.1.13    | Voltage              | $V_{\mathrm{SI\_GND}}$ | - 0.3 | 61       | V        | _                                                                                                                                                                                             |

| 4.1.14    | Current              | $I_{ m SI\_GND}$       | _     | _        | -        | -                                                                                                                                                                                             |

| Enable i  | nput ENABLE          |                        |       |          |          |                                                                                                                                                                                               |

| 4.1.15    | Voltage              | $V_{ENABLE}$           | - 0.3 | 61       | V        | IFX80471SKV                                                                                                                                                                                   |

| 4.1.16    | Current              | $I_{ENABLE}$           | _     | _        | V        | _                                                                                                                                                                                             |

| Sense c   | omparator input SI   | <u> </u>               |       | <u>'</u> |          |                                                                                                                                                                                               |

| 4.1.17    | Voltage              | $V_{SI}$               | - 0.3 | 61       | V        | _                                                                                                                                                                                             |

| 4.1.18    | Current              | $I_{SI}$               | _     | _        | V        | _                                                                                                                                                                                             |

| Sense c   | omparator output SO  | '                      | •     | 1        |          |                                                                                                                                                                                               |

| 4.1.19    | Voltage              | $V_{SO}$               | - 0.3 | 6.8      | V        | _                                                                                                                                                                                             |

| 4.1.20    | Current              | $I_{SO}$               | _     | _        | V        | limited internally                                                                                                                                                                            |

### Absolute Maximum Ratings (cont'd)<sup>1)</sup>

all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                                 | Symbol          | Limi  | t Values | Unit | Conditions         |

|---------|-------------------------------------------|-----------------|-------|----------|------|--------------------|

|         |                                           |                 | Min.  | Max.     |      |                    |

| Buck ou | utput voltage input VOUT                  |                 |       |          | '    |                    |

| 4.1.21  | Voltage                                   | $V_{VOUT}$      | - 0.3 | 15       | V    | IFX80471SKV        |

| 4.1.22  | Voltage                                   | $V_{VOUT}$      | - 0.3 | 6.8      | V    | IFX80471SKV50      |

| 4.1.23  | Current                                   | $I_{VOUT}$      | _     | _        | V    | _                  |

| Comper  | nsation input COMP                        |                 |       | ,        | '    |                    |

| 4.1.24  | Voltage                                   | $V_{COMP}$      | - 0.3 | 6.8      | V    | _                  |

| 4.1.25  | Current                                   | $I_{COMP}$      | _     | _        | V    | _                  |

| Reset o | utput RO                                  |                 | -     |          |      |                    |

| 4.1.26  | Voltage                                   | $V_{RO}$        | - 0.3 | 6.8      | V    | _                  |

| 4.1.27  | Current                                   | $I_{RO}$        | _     | _        | V    | limited internally |

| Frequer | ncy synchronization input SYNC            |                 | *     | *        |      |                    |

| 4.1.28  | Voltage                                   | $V_{SYNC}$      | - 0.3 | 6.8      | V    | _                  |

| 4.1.29  | Current                                   | $I_{SYNC}$      | _     | _        | V    | _                  |

| Temper  | atures                                    |                 |       |          | '    |                    |

| 4.1.30  | Junction Temperature                      | $T_{J}$         | -40   | 150      | °C   | _                  |

| 4.1.31  | Storage temperature                       | $T_{STG}$       | -50   | 150      | °C   | _                  |

| ESD Su  | sceptibility                              |                 |       | <u> </u> |      | -1                 |

| 4.1.32  | ESD Resistivity Pin $V_{OUT}$             | $V_{ESD\_VOUT}$ | -1.5  | 1.5      | kV   | HBM <sup>2)</sup>  |

| 4.1.33  | ESD Resistivity all Pins except $V_{OUT}$ | $V_{ESD}$       | -2    | 2        | kV   | HBM <sup>2)</sup>  |

| 4.1.34  | ESD Resistivity to GND                    | $V_{ESD}$       | -500  | 500      | V    | CDM <sup>3)</sup>  |

<sup>1)</sup> Not subject to production test, specified by design.

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

<sup>2)</sup> ESD susceptibility, HBM according to EIA/JESD 22-A114B

<sup>3)</sup> ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101 or ESDA STM5.3.1

### 4.2 Functional Range

### Table 1

| Pos.  | Parameter                               | Symbol                 | Symbol Limit V |                                     | Unit | Conditions                                                             |

|-------|-----------------------------------------|------------------------|----------------|-------------------------------------|------|------------------------------------------------------------------------|

|       |                                         |                        | Min.           | Max.                                |      |                                                                        |

| 4.2.1 | Supply Voltage Range                    | $V_{VS}$               | 5              | 60                                  | V    | _                                                                      |

| 4.2.2 | Output voltage adjust range IFX80471SKV | $V_{OUT}$              | 7              | 15                                  | V    | IFX80471SKV                                                            |

| 4.2.3 | Sense Resistor                          | $R_{SENSE}$            | 10             | 47                                  | mΩ   | Calculation see Chapter 7                                              |

| 4.2.4 | PMOS, on+off delay                      | $t_{ m on+off\ delay}$ | _              | t <sub>min</sub> -300 <sup>1)</sup> | ns   | $t_{\text{min}}$ = $V_{\text{VOUT}} / (V_{\text{VS}} * f_{\text{SW}})$ |

| 4.2.5 | Buck driver supply capacitor            | $C_{BDS}$              | 220            | _                                   | nF   | _                                                                      |

| 4.2.6 | Buck inductance                         | $L_1$                  | 22             | 100                                 | μΗ   | _2)                                                                    |

| 4.2.7 | Buck output capacitor                   | $C_{OUT}$              | 100            | _                                   | μF   | _                                                                      |

| 4.2.8 | Junction Temperature                    | $T_{i}$                | -40            | 125                                 | °C   | _                                                                      |

|       |                                         | •                      | 1              |                                     |      | _                                                                      |

<sup>1)</sup> A too high PMOS on+off delay might cause an instable output voltage

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

<sup>2)</sup> a recommended minimum value for  $L_1$  is 47 $\mu$ H

### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                                 | Symbol      | Limit Values Unit |      |      | Conditions |                |

|-------|-------------------------------------------|-------------|-------------------|------|------|------------|----------------|

|       |                                           |             | Min.              | Тур. | Max. |            |                |

| 4.3.1 | Junction to Soldering Point <sup>1)</sup> | $R_{thJSP}$ | _                 | 50   | _    | K/W        | _              |

| 4.3.2 | Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _                 | 140  | _    | K/W        | Footprint only |

<sup>1)</sup> Not subject to production test, specified by design.

### **5** Electrical Characteristics

### **5.1** Electrical Characteristics

### **Electrical Characteristics: Power**

| Pos.  | Parameter                               | Symbol            |      | Limit Val | lues           | Unit | Conditions                                                                                                                                                                                       |

|-------|-----------------------------------------|-------------------|------|-----------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                         |                   | Min. | Тур.      | Max.           |      |                                                                                                                                                                                                  |

| urren | nt Consumption <sup>1)</sup> IFX80471Sh | (V50              | •    |           | <del>- !</del> | •    |                                                                                                                                                                                                  |

| 5.1.1 | Current consumption of VS               | $I_{VS}$          | _    | 80        | 150            | μA   | $V_{\rm VS}$ = 48V;<br>PFM mode                                                                                                                                                                  |

|       |                                         |                   | _    | 70        | 85             | μΑ   | $V_{\rm VS}$ = 13.5V;<br>PFM mode;<br>$T_{\rm j}$ = 25 °C                                                                                                                                        |

| 5.1.2 | Current consumption of SI_ENABLE        | $I_{SI\_ENABLE}$  | _    | 9         | 30             | μΑ   | $V_{\rm VS}$ = 48V; $V_{\rm SI\_ENABLE}$ = 48V; PFM mode                                                                                                                                         |

| 5.1.3 | Current consumption of VOUT             | $I_{VOUT}$        | -    | 95        | 130            | μА   | $V_{\rm SI\_ENABLE} = \rm L;$<br>$V_{\rm VOUT} = 5.5 \rm V;$<br>$V_{\rm VS} = 13.5 \rm V;$<br>PFM mode;<br>$T_{\rm j} = 25 \rm ^{\circ} \rm C$                                                   |

|       |                                         |                   | _    | 140       | 220            | μА   | $\begin{split} &V_{\text{SI\_ENABLE}} = \text{H}; \\ &V_{\text{VOUT}} = 5.5\text{V}; \\ &V_{\text{VS}} = 13.5\text{V}; \\ &V_{\text{SI}} > V_{\text{SI, high}}; \\ &\text{PFM mode} \end{split}$ |

| 5.1.4 | Current consumption of SI               | $I_{\mathrm{SI}}$ | -    | 0.2       | 0.5            | μА   | $\begin{split} V_{\text{SI\_ENABLE}} &= \text{H}; \\ V_{\text{VS}} &= \text{13.5V}; \\ V_{\text{SI}} &= \text{10V}; \\ \text{PFM mode} \end{split}$                                              |

| urren | nt Consumption <sup>1)</sup> IFX80471SF | (V (variable      | )    |           |                |      |                                                                                                                                                                                                  |

| 5.1.5 | Current consumption of VS               | $I_{VS}$          | _    | 80        | 150            | μΑ   | $\begin{split} V_{\text{VS}} &= 48\text{V}; \\ V_{\text{ENABLE}} &= \text{H}; \\ \text{PFM mode}; \\ V_{\text{OUT}} &\geq 7\text{V} \end{split}$                                                 |

|       |                                         |                   | _    | 70        | 85             | μА   | $\begin{split} V_{\text{VS}} &= \text{13.5V}; \\ V_{\text{ENABLE}} &= \text{H}; \\ \text{PFM mode}; \\ T_{\text{j}} &= \text{25 °C}; \\ V_{\text{OUT}} &\geq \text{7V} \end{split}$              |

| 5.1.6 | Current consumption of VS               |                   | _    |           | 2              | μΑ   | $V_{\text{ENABLE}}$ = 0V;<br>$T_{\text{j}}$ < 105°C                                                                                                                                              |

| 5.1.7 | Current consumption of ENABLE           | $I_{EN}$          | _    | 9         | 30             | μA   | $\begin{split} V_{\text{VS}} &= 48 \text{V}; \\ V_{\text{ENABLE}} &= \text{H}; \\ \text{PFM mode} \end{split}$                                                                                   |

### Electrical Characteristics: Power (cont'd)

| Pos.   | Parameter                   | Symbol                       |       | Limit Val | ues   | Unit | Conditions                                                                                                                                                                                                                                                                     |

|--------|-----------------------------|------------------------------|-------|-----------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                             |                              | Min.  | Тур.      | Max.  |      |                                                                                                                                                                                                                                                                                |

| 5.1.8  | Current consumption of VOUT | $I_{VOUT}$                   | -     | 140       | 220   | μА   | $\begin{split} V_{\text{OUT}} &= 8\text{V}; \\ V_{\text{VS}} &= 13.5\text{V}; \\ V_{\text{ENABLE}} &= \text{H}; \\ V_{\text{SI}} &> V_{\text{SI, high}}; \\ \text{PFM mode} \end{split}$                                                                                       |

| 5.1.9  | Current consumption of SI   | $I_{\mathrm{SI}}$            | -     | 0.2       | 0.5   | μА   | $V_{\rm VS}$ = 13.5V;<br>$V_{\rm ENABLE}$ = H;<br>$V_{\rm SI}$ = 10V;<br>PFM mode;<br>$T_{\rm i}$ = 25°C                                                                                                                                                                       |

| 5.1.10 | Current consumption of FB   | $I_{FB}$                     | -     | 0.2       | 0.5   | μА   | $V_{\rm VS}$ = 13.5V;<br>$V_{\rm FB}$ = 1.25V;<br>$V_{\rm ENABLE}$ = H;<br>PFM mode;<br>$T_{\rm j}$ = 25°C                                                                                                                                                                     |

| Buck C | Controller                  |                              |       |           |       |      |                                                                                                                                                                                                                                                                                |

| 5.1.11 | Output voltage              | Output voltage $V_{ m VOUT}$ | 4.85  | 5.00      | 5.15  | V    | $\begin{split} & \text{IFX80471SKV50;} \\ & V_{\text{VS}} \! = \! 13.5 \text{V\& 48V;} \\ & \text{PWM mode} \\ & I_{\text{OUT}} = 0.5 \text{ to 2A;} \\ & R_{\text{SENSE}} = 22 \text{m}\Omega; \\ & R_{\text{M1}} = 0.25 \Omega; \\ & R_{\text{L1}} = 0.1 \Omega \end{split}$ |

|        |                             |                              | 4.75  | 5.00      | 5.25  | V    | $\begin{split} & \text{IFX80471SKV50;} \\ & V_{\text{VS}} = \text{24V; PFM mode;} \\ & I_{\text{OUT}} = \text{15mA;} \\ & R_{\text{SENSE}} = \text{22m}\Omega; \\ & R_{\text{M1}} = 0.25\Omega; \\ & R_{\text{L1}} = 0.1\Omega; \end{split}$                                   |

| 5.1.12 | FB threshold voltage        | $V_{FB,th}$                  | 1.225 | 1.25      | 1.275 | V    | IFX80471SKV                                                                                                                                                                                                                                                                    |

| 5.1.13 | Output voltage              | $V_{VOUT}$                   | 9.7   | 10.0      | 10.3  | V    | IFX80471SKV; Calibrated divider, see                                                                                                                                                                                                                                           |

|        |                             |                              | 9.5   | 10.0      | 10.5  | V    | IFX80471SKV; Calibrated divider, see                                                                                                                                                                                                                                           |

### Electrical Characteristics: Power (cont'd)

| Pos.   | Parameter                             | Symbol                                     | L                              | imit Valu                          | es                             | Unit     | Conditions                                                                                                                                                                                                                  |

|--------|---------------------------------------|--------------------------------------------|--------------------------------|------------------------------------|--------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                       |                                            | Min.                           | Тур.                               | Max.                           |          |                                                                                                                                                                                                                             |

| 5.1.14 | Buck output voltage adjust range      | $V_{VOUT}$                                 | $V_{FB,th}$                    | _                                  | 7                              | V        | IFX80471SKV, supplied by $V_{\rm S}$ only, complete current to supply the IC drawn from VS no reset function $^{2)}$                                                                                                        |

|        |                                       |                                            | 7                              | _                                  | 15                             | V        | IFX80471SKV, current to supply the IC drawn from VS and VOUT, as specified <sup>2)</sup>                                                                                                                                    |

| 5.1.15 | Buck output voltage accuracy          | $V_{VOUT}$                                 | 0.97 *<br>V <sub>OUT_nom</sub> | _                                  | 1.03 *<br>V <sub>OUT_nom</sub> |          | IFX80471SKV;<br>PWM mode <sup>2)</sup>                                                                                                                                                                                      |

| 5.1.16 | Buck output voltage accuracy          | $V_{VOUT}$                                 | 0.95 *<br>V <sub>OUT_nom</sub> | _                                  | 1.05 *<br>V <sub>OUT_nom</sub> |          | IFX80471SKV,<br>PFM mode <sup>2)</sup>                                                                                                                                                                                      |

| 5.1.17 | Line regulation                       | $ \Delta V_{VOUT} $                        | -                              | -                                  | 35                             | mV       | $\begin{split} & \text{IFX80471SKV50}, \\ & V_{\text{VS}} = \text{9V to 16V}; \\ & I_{\text{OUT}} = \text{1A}; \\ & R_{\text{SENSE}} = 22 \text{m}\Omega; \\ & \text{PWM mode} \end{split}$                                 |

|        |                                       |                                            | _                              | _                                  | 50                             | mV       | $\begin{split} & \text{IFX80471SKV50,} \\ & V_{\text{VS}} = \text{16V to 32V;} \\ & I_{\text{OUT}} = \text{1A;} \\ & R_{\text{SENSE}} = 22 \text{m}\Omega; \\ & \text{PWM mode} \end{split}$                                |

| 5.1.18 | Line regulation                       | $\Delta V_{ m VOUT}/V_{ m VOUT}$           | _                              | _                                  | 2.5                            | %        | $\begin{split} & \text{IFX80471SKV}, \\ & V_{\text{VS}} = \text{12V to 36V}; \\ & V_{\text{VOUT}} \text{=10V} \\ & I_{\text{OUT}} = \text{1A}; \\ & R_{\text{SENSE}} = 22 \text{m}\Omega; \\ & \text{PWM mode} \end{split}$ |

| 5.1.19 | Load regulation                       | $\Delta V_{ m VOUT}/$ $\Delta I_{ m LOAD}$ | -                              | 40                                 | -                              | mV/<br>A | $IFX80471SKV50; \\ I_{\rm OUT} = 0.5 {\rm A \ to \ 2A}; \ V_{\rm VS} = 5.8 {\rm V} \\ \& \ 48 {\rm V}; \\ R_{\rm SENSE} = 22 {\rm m} \Omega$                                                                                |

|        |                                       |                                            | -                              | 8 *<br>V <sub>OUT_nom</sub><br>/ V | -                              | mV/<br>A | $IFX80471SKV; \\ I_{\rm OUT} = 0.5 \text{ to } 2\text{A}; \\ V_{\rm VS} = 13.5\text{V \& } 4\text{8V}; \\ R_{\rm SENSE} = 22\text{m}\Omega$                                                                                 |

| 5.1.20 | Gate driver,<br>PMOS off              | $V_{\rm VS-} \ V_{\rm GDRV}$               | 0                              | -                                  | 0.2                            | V        | $\begin{split} V_{\text{ENABLE/Sl\_ENABLE}} &= 5 \text{ V}; \\ C_{\text{BDS}} &= 220 \text{ nF}; \\ C_{\text{GDRV}} &= 4.7 \text{nF} \end{split}$                                                                           |

| 5.1.21 | Gate driver,<br>PMOS on               | $V_{\rm VS-} \ V_{\rm GDRV}$               | 6                              | _                                  | 8.2                            | V        | $\begin{split} V_{\text{ENABLE/SI\_ENABLE}} &= 5 \text{ V}; \\ C_{\text{BDS}} &= 220 \text{ nF}; \\ C_{\text{GDRV}} &= 4.7 \text{nF}^{3)} \end{split}$                                                                      |

| 5.1.22 | Gate driver,<br>UV lockout            | $V_{\rm VS}$ – $V_{\rm BDS}$               | 2.75                           | _                                  | 4                              | V        | Decreasing ( $V_{\rm VS}\text{-}V_{\rm BDS}$ ) until GDRV is permanently at $VS$ level                                                                                                                                      |

| 5.1.23 | Gate driver, peak charging current    | $I_{GDRV}$                                 | _                              | 1                                  | _                              | A        | PMOS dependent; 2)                                                                                                                                                                                                          |

| 5.1.24 | Gate driver, peak discharging current | $I_{GDRV}$                                 | _                              | 1                                  | _                              | Α        | PMOS dependent; 2)                                                                                                                                                                                                          |

### **Electrical Characteristics: Power** (cont'd)

| Pos.   | Parameter                               | Symbol                                           | Limit Values               |                             |      | Unit | Conditions                                                                                                                                            |

|--------|-----------------------------------------|--------------------------------------------------|----------------------------|-----------------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                         |                                                  | Min.                       | Тур.                        | Max. |      |                                                                                                                                                       |

| 5.1.25 | Gate driver,<br>gate voltage, rise time | $t_{\rm r}$                                      | _                          | 45                          | 60   | ns   | $\begin{split} V_{\text{ENABLE/SI\_ENABLE}} &= 5 \text{ V}; \\ C_{\text{BDS}} &= 220 \text{ nF}; \\ C_{\text{GDRV}} &= 4.7 \text{nF} \end{split}$     |

| 5.1.26 | Gate driver,<br>gate voltage, fall time | $t_{f}$                                          | -                          | 50                          | 65   | ns   | $\begin{aligned} V_{\text{ENABLE/SI\_ENABLE}} &= 5 \text{ V}; \\ C_{\text{BDS}} &= 220 \text{ nF}; \\ C_{\text{GDRV}} &= 4.7 \text{nF} \end{aligned}$ |

| 5.1.27 | Peak current limit threshold voltage    | $V_{\text{LIM}} = V_{\text{VS}} - V_{\text{CS}}$ | 50                         | 70                          | 90   | mV   |                                                                                                                                                       |

| 5.1.28 | Oscillator frequency                    | $f_{ m OSC}$                                     | 290                        | 360                         | 420  | kHz  | PWM mode only                                                                                                                                         |

| 5.1.29 | Maximum duty cycle                      | $d_{MAX}$                                        | 100                        | -                           | _    | %    | PWM mode only                                                                                                                                         |

| 5.1.30 | Minimum on time                         | $t_{MIN}$                                        | _                          | 220                         | 400  | ns   | PWM mode only                                                                                                                                         |

| 5.1.31 | SYNC capture range                      | $\Delta f_{sync}$                                | 250                        | -                           | 530  | kHz  | PWM mode only                                                                                                                                         |

| 5.1.32 | SYNC trigger level high                 | $V_{SYNC,h}$                                     | 4.0                        | _                           | _    | V    | 2)                                                                                                                                                    |

| 5.1.33 | SYNC trigger level low                  | $V_{SYNC,I}$                                     | _                          | _                           | 0.8  | V    | 2)                                                                                                                                                    |

| Reset  | Generator                               |                                                  |                            |                             |      | I    |                                                                                                                                                       |

| 5.1.34 | Reset headroom                          | $V_{ m RT,HEAD}$                                 | 80                         | -                           | _    | mV   | $IFX80471SKV50; \\ V_{\rm OUT} (V_{\rm S}\text{=}6V, \\ I_{\rm LOAD}\text{=}1A) \\ -V_{\rm VOUT,RT}$                                                  |

| 5.1.35 | Reset threshold                         | $V_{ m VOUT,RT}$                                 | 4.5                        | 4.65                        | 4.8  | V    | IFX80471SKV50; $V_{\rm VOUT}$ increasing/decreasing                                                                                                   |

| 5.1.36 | Reset threshold hysteresis              | $\Delta V_{ m VOUT,RT}$                          | _                          | 50                          | _    | mV   | IFX80471SKV50 <sup>2)</sup>                                                                                                                           |

| 5.1.37 | Reset threshold                         | $V_{FB,RT}$                                      | -                          | 1.12                        | -    | V    | $\begin{array}{c} \text{IFX80471SKV;} \\ V_{\text{VOUT}} \text{ decreasing} \end{array}$                                                              |

|        |                                         |                                                  | _                          | 1.17                        | _    | V    | $\begin{array}{c} {\sf IFX80471SKV;} \\ V_{\sf VOUT} {\sf increasing} \end{array}$                                                                    |

| 5.1.38 | Reset output pull up resistor           | $R_{RO}$                                         | 10                         | 20                          | 40   | kΩ   | IFX80471SKV50; Internally connected to $V_{\mathrm{OUT}}$                                                                                             |

| 5.1.39 | Reset output High voltage               | $V_{RO,H}$                                       | 0.8 *<br>V <sub>VOUT</sub> | _                           | _    | V    | $I \hspace{-0.8em} \begin{array}{l} \text{IFX80471SKV50;} \\ I_{\text{RO}} = \text{0mA} \end{array}$                                                  |

| 5.1.40 | Reset output Low voltage                | $V_{RO,L}$                                       | _                          | 0.2                         | 0.4  | V    | $\begin{split} I_{\text{RO, L}} &= \text{1mA}; \\ \text{2.5V} &< V_{\text{VOUT}} < V_{\text{RT}} \end{split}$                                         |

|        |                                         |                                                  | _                          | 0.2                         | 0.4  | V    | $I_{\rm RO,L} = \rm 0.2mA; \\ 1V < V_{\rm VOUT} < \rm 2.5V$                                                                                           |

| 5.1.41 | Reset delay time                        | $t_{\sf rd}$                                     | 17                         | 21                          | 25   | ms   | IFX80471SKV                                                                                                                                           |

|        |                                         |                                                  | 70                         | 82                          | 100  | ms   | IFX80471SKV50                                                                                                                                         |

| 5.1.42 | Reset reaction time                     | $t_{rr}$                                         | _                          | _                           | 10   | μs   | 2)                                                                                                                                                    |

| Overvo | oltage Lockout                          |                                                  |                            |                             |      |      |                                                                                                                                                       |

| 5.1.43 | Overvoltage threshold                   | $V_{VOUT,OV}$                                    | _                          | V <sub>OUT_nom</sub> + 100  | _    | mV   | $\begin{array}{c} {\sf IFX80471SKV50;} \\ V_{\sf VOUT} {\sf increasing} \end{array}$                                                                  |

| 5.1.44 | Overvoltage threshold                   | $V_{FB,OV}$                                      | _                          | V <sub>FB,th,nom</sub> + 20 | _    | mV   | $\begin{array}{c} \text{IFX80471SKV;} \\ V_{\text{VOUT}} \text{ increasing} \end{array}$                                                              |

### **Electrical Characteristics: Power** (cont'd)

|         | Parameter                             | Symbol                | Limit Values                      |      |            | Unit     | Conditions                                                                                                                            |

|---------|---------------------------------------|-----------------------|-----------------------------------|------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

|         |                                       |                       | Min.                              | Тур. | Max.       |          |                                                                                                                                       |

| ENABL   | E Input                               |                       | 1                                 |      | "          |          |                                                                                                                                       |

| 5.1.45  | Enable ON-threshold                   | $V_{\rm enable,ON}$   | 4.5                               | _    | _          | V        |                                                                                                                                       |

| 5.1.46  | Enable OFF-threshold                  | $V_{\rm enable,OFF}$  | _                                 | _    | 0.8        | V        |                                                                                                                                       |

| SI_ENA  | ABLE Input                            | •                     | 1                                 |      |            | <b>"</b> |                                                                                                                                       |

| 5.1.47  | Enable ON-threshold                   | $V_{\rm enable,ON}$   | 4.5                               | _    | _          | V        |                                                                                                                                       |

| 5.1.48  | Enable OFF-threshold                  | $V_{\rm enable,OFF}$  | _                                 | _    | 8.0        | V        |                                                                                                                                       |

| SI_GNE  | ) Input                               |                       |                                   |      | -          | •        |                                                                                                                                       |

| 5.1.49  | Switch ON resistance                  | $R_{SW}$              | 50                                | 100  | 230        | Ω        | $V_{\text{SI\_ENABLE}}$ = 5V;<br>$I_{\text{SI\_GND}}$ = 3mA                                                                           |

| Battery | Voltage Sense                         |                       |                                   |      |            |          |                                                                                                                                       |

| 5.1.50  | Sense threshold                       | $V_{\mathrm{SI,low}}$ | 1.22                              | 1.25 | 1.28       | V        | V <sub>VS</sub> decreasing                                                                                                            |

| 5.1.51  | Sense threshold                       | $V_{ m SI,high}$      | _                                 | 1.33 | _          | V        | V <sub>VS</sub> increasing                                                                                                            |

| 5.1.52  | Sense threshold hysteresis            | $V_{ m SI,hys}$       | 30                                | 80   | 120        | mV       |                                                                                                                                       |

| 5.1.53  | Sense output pull up resistor         | $R_{SO}$              | 10                                | 20   | 40         | kΩ       | IFX80471SKV50; Internally connected to $V_{\mathrm{VOUT}}$                                                                            |

| 5.1.54  | Sense out output High voltage         | $V_{SO,H}$            | 0.8 *<br><i>V</i> <sub>VOUT</sub> |      |            | V        | $I_{\mathrm{SO,H}}$ =0mA                                                                                                              |

| 5.1.55  | Sense out output Low voltage          | $V_{SO,L}$            |                                   | 0.2  | 0.4        | V        | $I_{\rm SO,L}$ = 1mA;<br>2.5V < $V_{\rm VOUT}$ ; $V_{\rm SI}$ < 1.13 V                                                                |

|         |                                       |                       |                                   | 0.4  | $V_{VOUT}$ | V        | $\begin{split} &I_{\rm SOL} \text{=0.2mA;} \\ &1 \text{V} < V_{\rm VOUT} < 2.5 \text{V;} \\ &V_{\rm SI} < 1.13 \text{ V} \end{split}$ |

| Therma  | al Shutdown                           |                       | •                                 | •    | •          |          |                                                                                                                                       |

| 5.1.56  | Thermal shutdown junction temperature | $T_{\rm jSD}$         | 150                               | 175  | 200        | °C       | 2)                                                                                                                                    |

| 5.1.57  | Temperature hysteresis                | ΔΤ                    |                                   | 30   |            | K        | 2)                                                                                                                                    |

<sup>1)</sup> The device current measurements for  $I_{\rm VS}$  and  $I_{\rm FB}$  exclude MOSFET driver currents.

<sup>2)</sup> Not subject to production test - specified by design

<sup>3)</sup> For 4V <  $V_{\rm VS}$  < 6V:  $V_{\rm GDRV}$  pprox 0V.

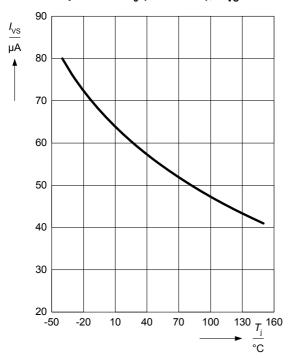

### 5.2 Typical Performance Characteristics

### **Typical Performance Characteristics**

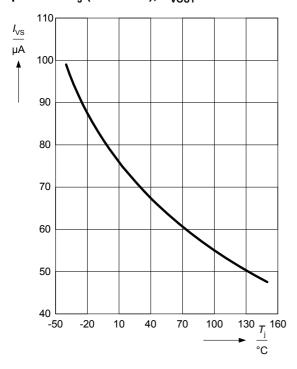

Current Consumption  $I_{\rm VS}$  versus Junction Temperature  $T_{\rm J}$  (INH = ON),  $V_{\rm VS}$  = 13.5 V

Current Consumption  $I_{\rm VS}$  versus Junction Temperature  $T_{\rm J}$  (INH = ON),  $V_{\rm VOUT}$  = 48 V

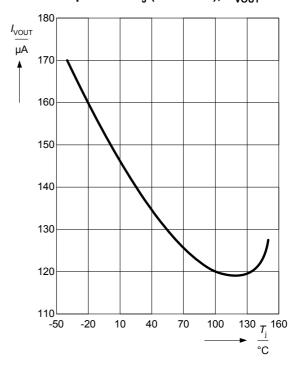

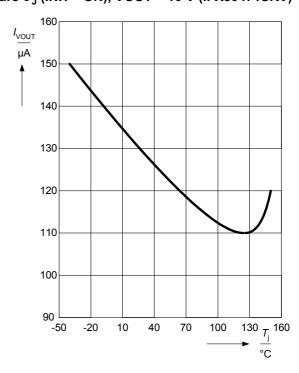

## Current Consumption $I_{\rm VOUT}$ versus Junction Temperature $T_{\rm J}$ (INH = ON), $V_{\rm VOUT}$ = 5.5 V

## Current Consumption $I_{\text{VOUT}}$ vs. Junction Temperature $T_{\text{J}}$ (INH = ON), VOUT = 10 V (IFX80471SKV)

# Internal oscillator frequency $f_{OSC}$ versus Junction Temperature $T_i$ )

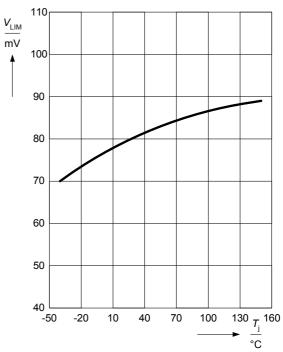

# Peak current limit threshold voltage $V_{\rm LIM}$ versus Junction Temperature $T_{\rm j}$

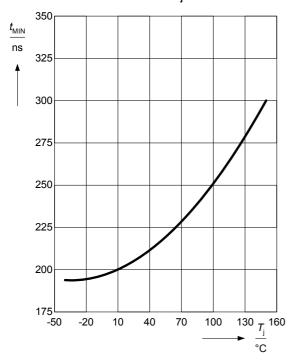

## Minimum on time $t_{MIN}$ (blanking) versus Junction Temperature $T_{i}$

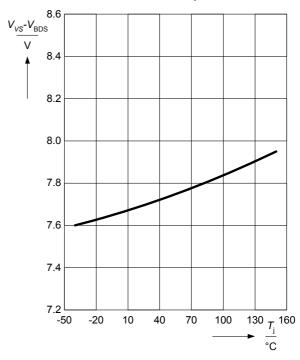

## Gate driver supply $V_{ m VS}$ - $V_{ m BDS}$ versus Junction Temperature $T_{ m i}$

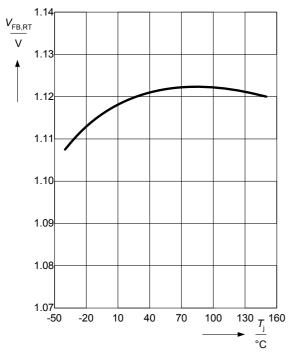

## Lower Reset threshold $V_{\rm FB,RT}$ versus Junction Temperature $T_{\rm i}$ (IFX80471SKV)

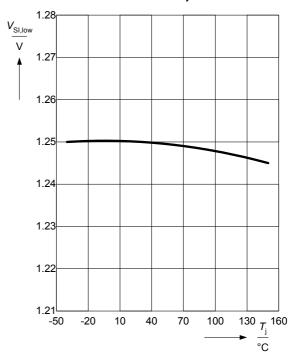

## Lower Sense threshold $V_{\rm SI}$ , low versus Junction Temperature $T_{\rm i}$

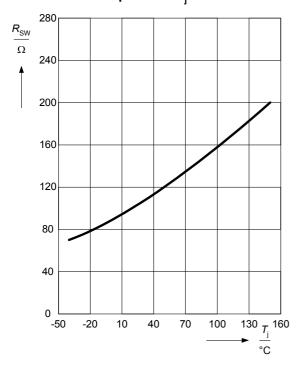

# On resistance of SI\_GND switch $R_{\rm SW}$ versus Junction Temperature $T_{\rm i}$

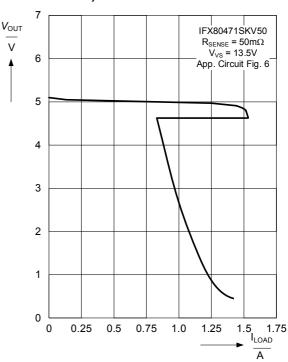

## Output Voltage versus Load Current (IFX80471SKV50)

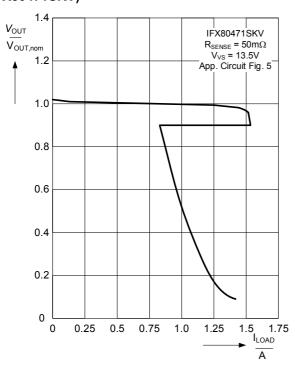

## Output voltage vs. Load Current (IFX80471SKV)

**Detailed Circuit Description**

### 6 Detailed Circuit Description

In the following, the internal blocks of the IFX80471 are described in more detail. For selecting external components please refer to the section "Application Information" on Page 21.

### 6.1 PFM/PWM Step-down regulator

To meet also high requirements in terms of current consumption a special PFM (Pulse Frequency Modulation) - PWM (Pulse Width Modulation) control scheme for highest efficiency is implemented in the IFX80471 regulators. Under light load conditions the output voltage is able to increase slightly and at a certain threshold the controller jumps into PFM mode. In this PFM operation the PMOS is triggered with a certain on time (depending on input voltage, output voltage, inductance- and sense resistor value) whenever the buck output voltage decreases to the so called WAKE-threshold. The switching frequency of the step down regulator is determined in the PFM mode by the load current. It increases with increasing load current and turns finally to the fixed PWM frequency at a certain load current depending on the input voltage, current sense resistor and inductance. The diagram below shows the buck regulation circuit of the IFX80471.

Figure 3 Buck control scheme

The IFX80471 uses a slope-compensated peak current mode PWM control scheme in which the feedback or output voltage of the step down circuit and the peak current of the current through the PMOS are compared to form the OFF signal for the external PMOS. The ON-trigger is set periodically by the internal oscillator when acting in PWM mode and is given by the output of the WAKE-comparator when operating in PFM mode. The Multiplexer (MUX) is switched by the output of the MODE-detector which distinguishes between PFM and PWM by tracking the output voltage (go to PFM) and by tracking the gate trigger frequency (goto PWM). In PFM mode the peak current limit is reduced to prevent overshoots at the output of the buck regulator. In order to avoid a gate turn off signal due to the current peak caused by the parasitic capacitance of the catch diode the blanking filter is necessary. The blanking time is set internally to 200ns and determines (together with the PMOS turn on and turn off delay) the minimum duty cycle of the device. In addition to the PFM/PWM regulation scheme an overvoltage lockout and thermal protection are implemented to guarantee safe operation of the device and of the supplied application circuit.

**Detailed Circuit Description**

### 6.2 Battery voltage sense

To detect undervoltage conditions at the battery a sense comparator block is available within the IFX80471. The voltage at the SI input is compared to an internal reference of typ. 1.25V. The output of the comparator drives a NMOS structure giving a low signal at SO as soon as the voltage at SI decreases below this threshold. In the 5V fixed version an internal pull up resistor is connected from the drain of the NMOS to the output of the buck converter, in the variable version SO is open drain.

The sense in voltage divider can be switched to high impedance by a low signal at the SI\_ENABLE to avoid high current consumption to GND (IFX80471SKV50 only).

Of course the sense comparator can be used for any input voltage and does not have to be used for the battery voltage sense only.

### 6.3 Undervoltage Reset

The output voltage is monitored continuously by the internal undervoltage reset comparator. As soon as the output voltage decreases below the thresholds given in the characteristics the NPN structure pulls RO low (latched). In the 5V fixed version an internal pull up resistor is connected from the collector of the NPN to the output of the buck converter, in the variable version RO is open collector.

At power up RO is kept low until the output voltage has reached its reset threshold and stayed above this threshold for the power on reset delay time.

### 7 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

#### 7.1 General

The IFX80471 step-down DC-DC controllers are designed primarily for use in industrial applications and offer a large flexibility in the input voltage range they can handle. Using an external P-MOSFET and current-sense resistor allows design flexibility and the improved efficiencies associated with high-performance P-channel MOSFETs. The unique, peak current-limited, PWM/PFM control scheme gives these devices excellent efficiency over wide load ranges, while drawing around 100µA current from the battery under no load condition. This wide dynamic range optimizes the IFX80471 for applications, where load currents can vary considerably as individual circuit blocks are turned on and off to conserve energy. Operation to a 100% duty cycle allows the lowest possible dropout voltage, maintaining operation during cold cranking. High switching frequencies and a simple circuit topology minimize PC board area and component costs.

### 7.2 Output voltage at adjustable version - feedback divider

The output voltage is sensed either by an internal voltage divider connected to the VOUT pin (IFX80471SKV50, fixed 5V version) or an external divider from the Buck output voltage to the FB pin (IFX80471SKV, adjustable version). The Vout pin has to be connected always to the Buck converter output regardless which output voltage for the adjustable version is desired.

To determine the resistors of the feedback divider for the desired output voltage  $V_{OUT}$  at the IFX80471SKV select  $R_{FB2}$  between  $5k\Omega$  and  $500k\Omega$  and obtain  $R_{FB1}$  with the following formula:

$$R_{FB1} = R_{FB2} \cdot \left(\frac{V_{OUT}}{V_{FB, th}} - 1\right)$$

$V_{FB}$  is the threshold of the error amplifier with its value of typical 1.25V which shows that the output voltage can be adjusted in a range from 1.25V to 15V. However the integrated Reset function will only be operational if the output voltage level is adjusted to >7V.

Also the current consumption will be increased in PFM mode in the range between 1.25V and 7V.

### 7.3 SI Enable

Connecting SI\_ENABLE to 5V causes SI\_GND to have low impedance. Thus the SI comparator is in operation and can be used to monitor the battery voltage. SO output signal is valid. Connecting SI\_ENABLE to GND causes SI\_GND to have high impedance. Thus the SI comparator is not able to monitor the battery voltage. SO output signal is invalid.

### 7.3.1 Battery sense comparator - voltage divider

The formula to calculate the resistor divider for the sense comparator is basically the same as for the feedback divider in section before. With the selected resistor  $R_{Sl2}$ , the desired threshold of the input voltage  $V_{IN,\ UV}$  and the lower sense threshold  $V_{Sl.\ low}$  the resistor  $R_{Sl1}$  is given to:

$$R_{SI1} = R_{SI2} \cdot \left( \frac{V_{IN, UV}}{V_{SI, low}} - 1 \right)$$

For high accuracy and low ohmic resistor divider values the on-resistance of the SI\_GND NMOS (typ.  $100\Omega$ ) has to be added to  $R_{SI2}$ .

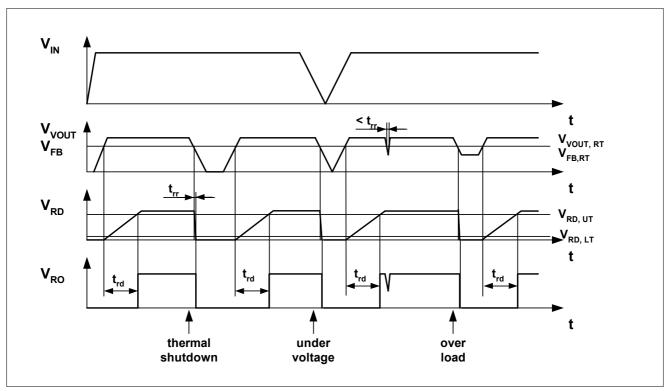

### 7.4 Undervoltage reset - delay time

The diagram below shows the typical behavior of the reset output in dependency on the input voltage  $V_{IN}$ , the output voltage  $V_{VOUT}$  or  $V_{FB}$ .

Figure 4 Reset timing

### 7.5 100% duty-cycle operation and dropout

The IFX80471 operates with a duty cycle up to 100%. This feature allows to operate with the lowest possible drop voltage at low battery voltage as it occurs at cold cranking. The MOSFET is turned on continuously when the supply voltage approaches the output voltage level, conventional switching regulators with less than 100% duty cycle would fail in that case.

The drop- or dropout voltage is defined as the difference between the input and output voltage levels when the input is low enough to drop the output out of regulation. Dropout depends on the MOSFET drain-to-source on-resistance, the current-sense resistor and the inductor series resistance. It is proportional to the load current:

$$V_{drop} = I_{LOAD} \cdot (R_{DS(ON)PMOS} + R_{SENSE} + R_{INDUCTANCE})$$

### 7.6 SYNC Input and Frequency Control

The IFX80471's internal oscillator is set for a fixed PWM switching frequency of 360kHz or can be synchronized to an external clock at the SYNC pin. When the internal clock is used SYNC has to be connected to GND. SYNC is a negative-edge triggered input that allows synchronization to an external frequency ranging between 270kHz and 530kHz. When SYNC is clocked by an external signal, the converter operates in PWM mode until the load current drops below the PWM to PFM threshold. Thereafter the converter continues operation in PFM mode.

#### 7.7 Shutdown Mode

Connecting ENABLE to GND places the IFX80471SKV in shutdown mode. In shutdown, the reference, control circuitry, external switching MOSFET, and the oscillator are turned off and the output falls to 0V. Connect ENABLE to voltages higher than 4.5V for normal operation. As this input operates analogue way the voltage applied at this pin should have a slope of 0.5V/3µs as a minimum requirement to avoid undefined states within the device.

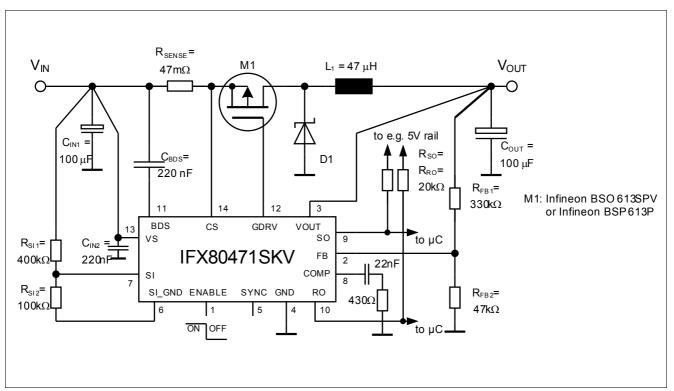

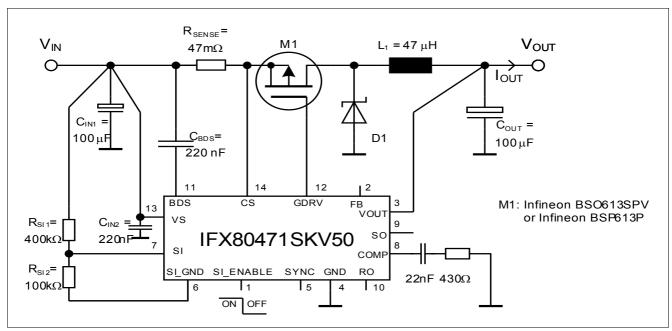

#### 7.8 Buck converter circuit

A typical choice of external components for the buck converter circuit is given in **Figure 5** and **Figure 6**. For basic operation of the buck converter the input capacitors  $C_{IN1}$ ,  $C_{IN2}$ , the driver supply capacitor  $C_{BDS}$ , the sense resistor  $R_{SENSE}$ , the PMOS device, the catch diode D1, the inductance L1 and the output capacitor  $C_{OUT}$  are necessary. In addition for low electromagnetic emission a Pi-filter at the input and/or a small resistor in the path between GDRV and the gate of the PMOS may be necessary.

#### 7.8.1 Buck inductance (L1) selection in terms of ripple current

The internal PWM/PFM control loop includes a slope compensation for stable operation in PWM mode. This slope compensation is optimized for inductance values of  $47\mu$ H and Sense resistor values of  $47m\Omega$  for the 5V output voltage versions. When choosing an inductance different from  $47\mu$ H the Sense resistor has to be changed also:

$$\frac{R_{SENSE}}{I.1} = (0.5...1.0) \times 10^{3} \frac{\Omega}{H}$$

Increasing this ratio above 1000  $\Omega$ /H may result in sub harmonic oscillations as well-known for peak current mode regulators without integrated slope compensation.

To achieve the same effect of slope compensation in the adjustable voltage version also the inductance in  $\mu H$  is given by

$$\left(2.0 \times 10^{-4} \cdot \frac{H}{V\Omega} \cdot V_{OUT} \cdot R_{SENSE}\right) < L1 < \left(4.0 \times 10^{-4} \cdot \frac{H}{V\Omega} \cdot V_{OUT} \cdot R_{SENSE}\right)$$

The inductance value determines together with the input voltage, the output voltage and the switching frequency the current ripple which occurs during normal operation of the step down converter. This current ripple is important for the all over ripple at the output of the switching converter.

$$\Delta I = \frac{(V_{IN} - V_{OUT}) \cdot V_{OUT}}{f_{SW} \cdot V_{IN} \cdot L1}$$

In this equation  $f_{sw}$  is the actual switching frequency of the device, given either by the internal oscillator or by an external source connected to the SYNC pin. When picking finally the inductance of a certain supplier (Epcos, Coilcraft etc.) the saturation current has to be considered. The saturation current value of the desired inductance has to be higher than the maximum peak current which can appear in the actual application.

### 7.8.2 Determining the current limit

The peak current which the buck converter is able to provide is determined by the peak current limit threshold voltage  $V_{LIM}$  and the sense resistor  $R_{SENSE}$ . With a maximum peak current given by the application ( $I_{PEAK}$ ,  $PWM = I_{LOAD} + 0.5\Delta I$ ) the sense resistor is calculated to

$$R_{SENSE} = \frac{V_{LIM}}{2 \cdot I_{DEAK, DWM}}$$

The equation above takes account for the foldback characteristic of the current limit as shown in the figures 'Output Voltage versus Load Current' on page 17/18 by introducing a factor of 2. It must be assured by correct dimensioning of R<sub>SENSE</sub> that the load current doesn't reach the foldback part of the characteristic curve.

#### 7.8.3 PFM and PWM thresholds

The crossover thresholds PFM to PWM and vice versa strongly depend on the input voltage  $V_{IN}$ , the Buck converter inductance L1, the sense resistor value  $R_{SENSE}$  and the turn on and turn off delays of the external PMOS.

### 7.8.4 Buck output capacitor ( $C_{OUT}$ ) selection:

The choice of the output capacitor effects straight to the minimum achievable ripple which is seen at the output of the buck converter. In continuous conduction mode the ripple of the output voltage can be estimated by the following equation:

$$V_{Ripple} = \Delta I \cdot \left( R_{ESRCOUT} + \frac{1}{8 \cdot f_{SW} \cdot C_{OUT}} \right)$$

From the formula it is recognized that the ESR has a big influence in the total ripple at the output, so low ESR tantalum or ceramic capacitors are recommended for the application (recommended range: 50mOhm to 150mOhm).

One other important thing to note are the requirements for the resonant frequency of the output LC-combination. The choice of the components L and C have to meet also the specified range given in **Chapter 4.2** otherwise instabilities of the regulation loop might occur.

### 7.8.5 Input capacitor $(C_{IN1})$ selection:

At high load currents, where the current through the inductance flows continuously, the input capacitor is exposed to a square wave current with its duty cycle  $V_{OUT}/V_I$ . To prevent a high ripple to the battery line a capacitor with low ESR should be used. The maximum RMS current which the capacitor has to withstand is calculated to:

$$I_{RMS} = I_{LOAD} \cdot \sqrt{\frac{V_{OUT}}{V_{IN}}} \cdot \sqrt{1 + \frac{1}{3} \cdot \left(\frac{\Delta I}{2 \cdot I_{LOAD}}\right)^2}$$

For low ESR an e.g. Al-electrolytic capacitance in parallel to an ceramic capacitance could be used.

### 7.8.6 Freewheeling diode / catch diode (D1)

For lowest power loss in the freewheeling path Schottky diodes are recommended. With those types the reverse recovery charge is negligible and a fast hand over from freewheeling to forward conduction mode is possible. Depending on the application (12V battery systems) 40V types could be also used instead of the 60V diodes. Also for high temperature operation select a Schottky-diode with low reverse leakage.

A fast recovery diode with recovery times in the range of 30ns can be also used if smaller junction capacitance values (smaller spikes) are desired.

### 7.8.7 Buck driver supply capacitor ( $C_{BDS}$ )

The voltage at the ceramic capacitor is clamped internally to 7V, a ceramic type with a minimum of 220nF and voltage class 16V would be sufficient.

### 7.8.8 Input pi-filter components for reduced EME