## Multi-band RF frequency synthesizer with integrated VCOs

### **Features**

- Integer-N frequency synthesizer

- Dual differential integrated VCOs with automatic center frequency calibration:

- 2500 3050 MHz (direct output)

- 4350 5000 MHz (direct output)

- 1250 1525 MHz (internal divider by 2)

- 2175 2500 MHz (internal divider by 2)

- 625 762.5 MHz (internal divider by 4)

- 1087.5 1250 MHz (internal divider by 4)

- Excellent integrated phase noise

- Fast lock time: 150µs

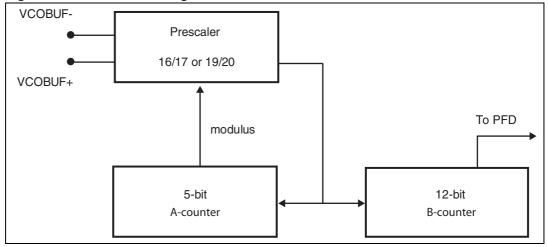

- Dual modulus programmable prescaler (16/17 or 19/20)

- 2 programmable counters to achieve a feedback division ratio from 256 to 65551 (prescaler 16/17) and from 361 to 77836 (prescaler 19/20).

- Programmable reference frequency divider (10 bits)

- Phase frequency comparator and charge pump

- Programmable charge pump current

- Digital lock detector

- Dual digital bus interface: SPI and I<sup>2</sup>C bus (fast mode) with 3 bit programmable address (1100A<sub>2</sub>A<sub>1</sub>A<sub>0</sub>)

- 3.3 V power supply

- Power down mode (hardware and software)

- Small size exposed pad VFQFPN28 package5 mm x 5 mm x 1.0 mm

- Process: BICMOS 0.35 µm SiGe

### **Applications**

- 2.5G and 3G Cellular infrastructure equipment

- CATV equipment

- Instrumentation and test equipment

- Other wireless communication systems

### **Description**

The STMicroelectronics STW81103 is an integrated RF synthesizer with voltage controlled oscillators (VCOs). Showing high performance, high integration, low power, and multi-band performances, STW81103 is a low cost one chip alternative to discrete PLL and VCOs solutions.

STW81103 includes an Integer-N frequency synthesizer and two fully integrated VCOs featuring low phase noise performance and a noise floor of -155dBc/Hz. The combination of wide frequency range VCOs (thanks to centerfrequency calibration over 32 sub-bands) and multiple output options (direct output, divided by 2 or divided by 4) allows to cover the 625 MHz-762.5 MHz, the 1087.5 MHz-1525 MHz, the 2175 MHz-3050 MHz and the 4350 MHz-5000 MHz bands.

The STW81103 is designed with STMicroelectronics advanced 0.35 µm SiGe process.

Contents STW81103

# **Contents**

| 1 | Bloc               | k diagram and pin configuration     |

|---|--------------------|-------------------------------------|

|   | 1.1                | Block diagram                       |

|   | 1.2                | Pin configuration                   |

| 2 | Elect              | trical specifications9              |

|   | 2.1                | Absolute maximum ratings            |

|   | 2.2                | Operating conditions 9              |

|   | 2.3                | Digital logic levels                |

|   | 2.4                | Electrical specifications 10        |

|   | 2.5                | Phase noise specification           |

| 3 | Туріс              | cal performance characteristics15   |

| 4 | Gene               | eral description                    |

| 5 | Circu              | uit description                     |

|   | 5.1                | Reference input stage               |

|   | 5.2                | Reference divider                   |

|   | 5.3                | Prescaler 19                        |

|   | 5.4                | A and B counters                    |

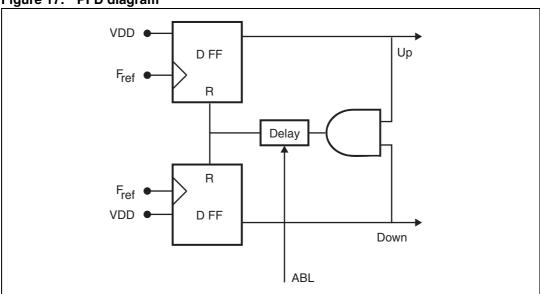

|   | 5.5                | Phase frequency detector (PFD)      |

|   | 5.6                | Lock detect                         |

|   | 5.7                | Charge pump                         |

|   | 5.8                | Voltage controlled oscillators      |

|   |                    | 5.8.1 VCO selection                 |

|   |                    | 5.8.2 VCO frequency calibration     |

|   |                    | 5.8.3 VCO voltage amplitude control |

|   | 5.9                | Output stage                        |

|   |                    | 5.9.1 Output buffer control mode    |

|   | 5.10               | External VCO buffer                 |

| 6 | I <sup>2</sup> C b | us interface                        |

|   | 6.1                | General features                    |

STW81103 Contents

|    |      | 6.1.1                | Data validity                        |

|----|------|----------------------|--------------------------------------|

|    |      | 6.1.2                | START and STOP conditions            |

|    |      | 6.1.3                | Byte format and acknowledge28        |

|    |      | 6.1.4                | Device addressing                    |

|    |      | 6.1.5                | Single-byte write mode29             |

|    |      | 6.1.6                | Multi-byte write mode                |

|    |      | 6.1.7                | Current byte address read mode       |

|    | 6.2  | Timing               | specification 30                     |

|    | 6.3  | I <sup>2</sup> C reg | gisters 32                           |

|    |      | 6.3.1                | Write-only registers                 |

|    |      | 6.3.2                | Read-only register 34                |

|    |      | 6.3.3                | Default configuration34              |

|    | 6.4  | VCO c                | alibration procedure                 |

|    |      | 6.4.1                | VCO calibration auto-restart feature |

| 7  | SPI  | digital ir           | nterface                             |

|    | 7.1  | Genera               | al features                          |

|    | 7.2  | Timing               | specification                        |

|    | 7.3  | Bit tabl             | es                                   |

|    |      | 7.3.1                | Default configuration                |

|    | 7.4  | VCO c                | alibration procedure                 |

|    |      | 7.4.1                | VCO calibration auto-restart feature |

| 8  | Арр  | lication             | information 41                       |

|    | 8.1  |                      | output                               |

|    | 8.2  |                      | d by 2 output                        |

|    | 8.3  |                      | d by 4 output                        |

|    | 8.4  |                      | tion kit                             |

| 9  | Арр  | lication             | diagram                              |

| 10 | Pack | kage me              | chanical data                        |

| 11 | Orde | ering inf            | ormation 52                          |

| 12 | Revi | sion his             | story 52                             |

|    |      |                      |                                      |

List of tables STW81103

# List of tables

| l able 1. | Pin description                                                 | /    |

|-----------|-----------------------------------------------------------------|------|

| Table 2.  | Absolute maximum ratings                                        | 9    |

| Table 3.  | Operating conditions                                            | 9    |

| Table 4.  | Digital logic levels                                            | . 10 |

| Table 5.  | Electrical specifications                                       | . 10 |

| Table 6.  | Phase noise specification · · · · · · · · · · · · · · · · · · · | 13   |

| Table 7.  | Current value vs. selection                                     | . 22 |

| Table 8.  | VCO A performances versus amplitude setting (Freq = 2.8 GHz)    | . 24 |

| Table 9.  | VCO B performances vs. amplitude setting (Freq = 4.7 GHz)       | . 25 |

| Table 10. | EXT_PD pin function setting                                     | . 25 |

| Table 11. | Single-byte write mode                                          | . 29 |

| Table 12. | Multi-byte write mode                                           | . 29 |

| Table 13. | Current byte address read mode                                  | . 29 |

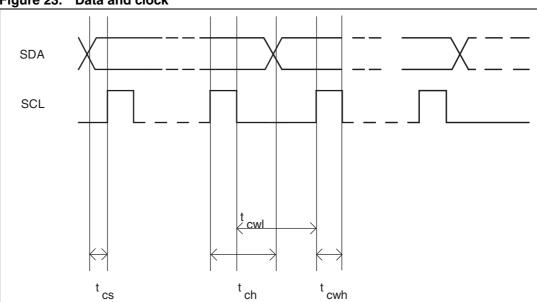

| Table 14. | Data and clock timing specifications                            | . 30 |

| Table 15. | Start and stop timing specifications                            | . 31 |

| Table 16. | Ack timing specifications                                       | . 31 |

| Table 17. | Write-only registers                                            | . 32 |

| Table 18. | Functional modes                                                | . 32 |

| Table 19. | SPI data structure (MSB is sent first)                          | . 37 |

| Table 20. | Address decoder and outputs                                     | . 37 |

| Table 21. | SPI timing specification                                        | . 37 |

| Table 22. | Bits at 00h and ST1                                             | . 38 |

| Table 23. | Bits at 01h and ST2                                             | . 39 |

| Table 24. | Order code of the evaluation kit                                | . 46 |

| Table 25. | Package dimensions                                              | . 51 |

| Table 26. | Order codes                                                     | . 52 |

| Tahla 27  | Document revision history                                       | 52   |

STW81103 List of figures

# **List of figures**

| Figure 1.                | Block diagram                                                        | . 6  |

|--------------------------|----------------------------------------------------------------------|------|

| Figure 2.                | Pin connection (top view)                                            | . 7  |

| Figure 3.                | VCO A (direct output) open loop phase noise                          | . 15 |

| Figure 4.                | VCO B (direct output) open loop phase noise                          | 15   |

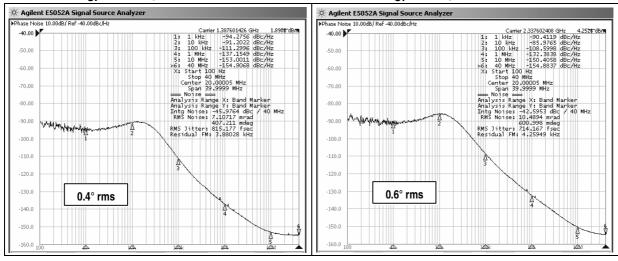

| Figure 5.                | VCO A (direct output) closed loop phase noise at 2.775 GHz           |      |

| (FSTEP=200               | 0 kHz; FPFD=200 kHz; ICP=2 mA)                                       | . 15 |

| Figure 6.                | VCO B (direct output) closed loop phase noise at 4.675 GHz           |      |

| (FSTEP=200               | 0 kHz; FPFD=200 kHz; ICP=3 mA)                                       | . 15 |

| Figure 7.                | VCO A (div. by 2 output) closed loop phase noise at 1.3876 GHz       |      |

| (FSTEP=200               | 0 kHz; FPFD=400 kHz; ICP=1.5 mA)                                     | 16   |

| Figure 8.                | VCO B (div. by 2 output) closed loop phase noise at 2.3376 GHz       |      |

| (FSTEP=200               | 0 kHz; FPFD=400 kHz; ICP=2 mA)                                       | 16   |

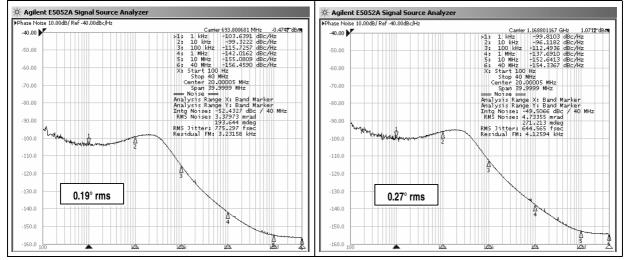

| Figure 9.                | VCO A (div. by 4 output) closed loop phase noise at 693.8 MHz        |      |

| (FSTEP=200               | 0 kHz; FPFD=800 kHz; ICP=1 mA)                                       | 16   |

| Figure 10.               | VCO B (div. by 4 output) closed loop phase noise at 1168.8 MHz       |      |

| (FSTEP=200               | 0 kHz; FPFD=800 kHz; ICP=1.5 mA)                                     | 16   |

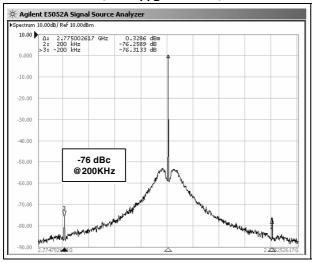

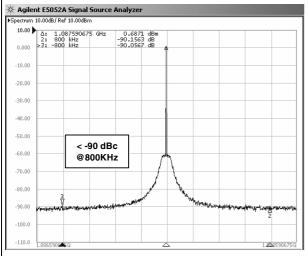

| Figure 11.               | PFD frequency spurs (direct output; FPFD=200 kHz)                    |      |

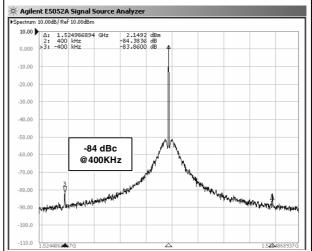

| Figure 12.               | PFD frequency spurs (div. by 2 output; FPFD=400 kHz)                 |      |

| Figure 13.               | PFD frequency spurs (div. by 4 output; FPFD=800 kHz)                 |      |

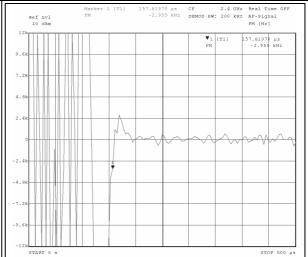

| Figure 14.               | Settling time (final frequency=2.4 GHz; FPFD=400 kHz; ICP=2.5 mA)    |      |

| Figure 15.               | Reference frequency input buffer                                     |      |

| Figure 16.               | VCO divider diagram                                                  |      |

| Figure 17.               | PFD diagram                                                          |      |

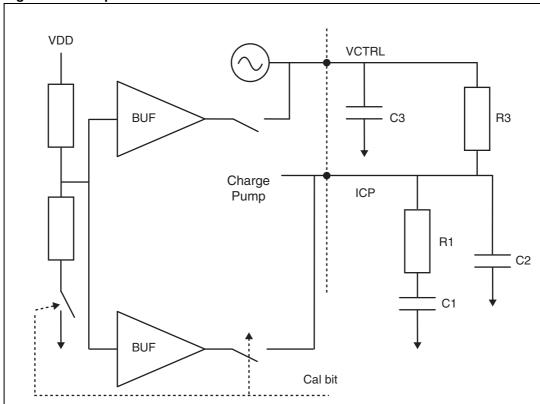

| Figure 18.               | Loop filter connection                                               |      |

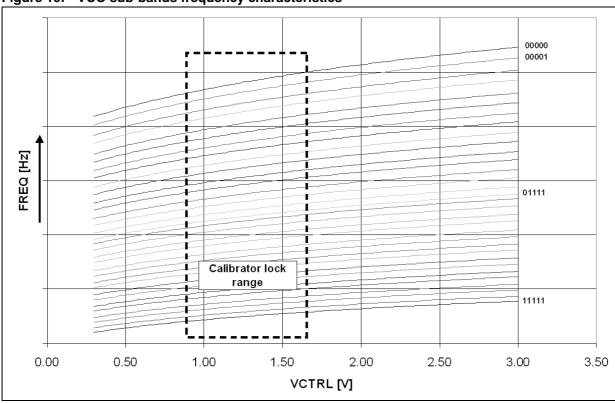

| Figure 19.               | VCO sub-bands frequency characteristics                              |      |

| Figure 20.               | Data validity                                                        |      |

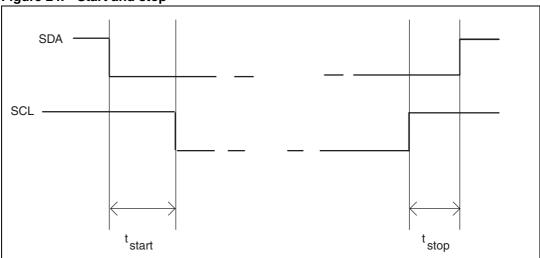

| Figure 21.               | START and STOP conditions                                            |      |

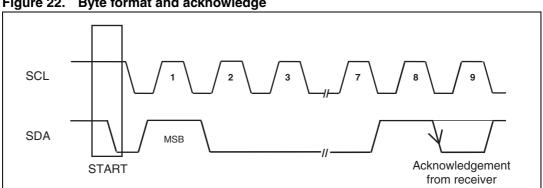

| Figure 22.               | Byte format and acknowledge                                          |      |

| Figure 23.               | Data and clock                                                       |      |

| Figure 24.               | Start and stop                                                       |      |

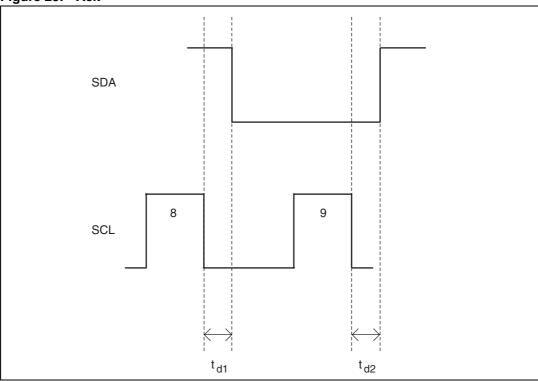

| Figure 25.               | Ack                                                                  |      |

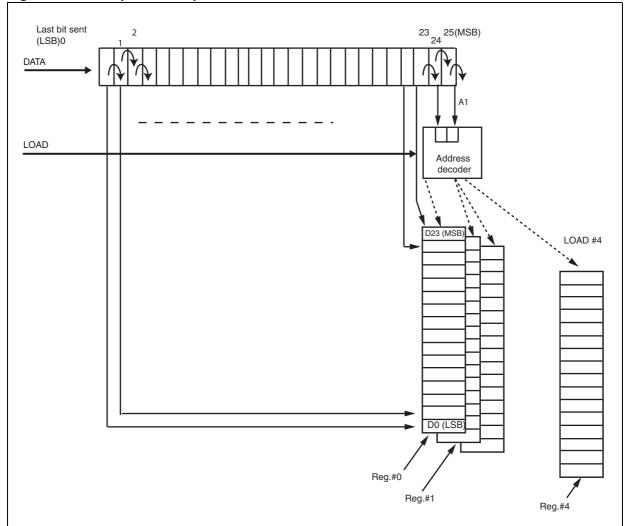

| Figure 26.               | SPI input and output bit order                                       |      |

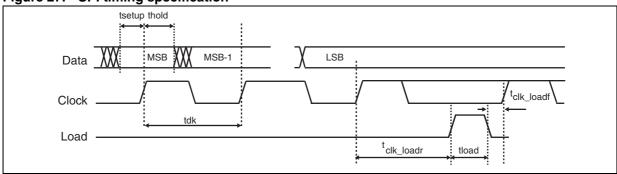

| Figure 27.               | SPI timing specification.                                            |      |

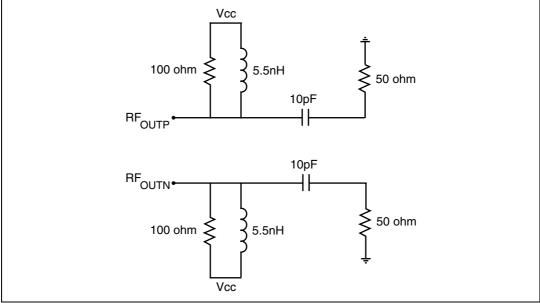

| Figure 28.               | Differential/single-ended output network (MATCH_LC_LUMP_4G_DIFF.dsn) |      |

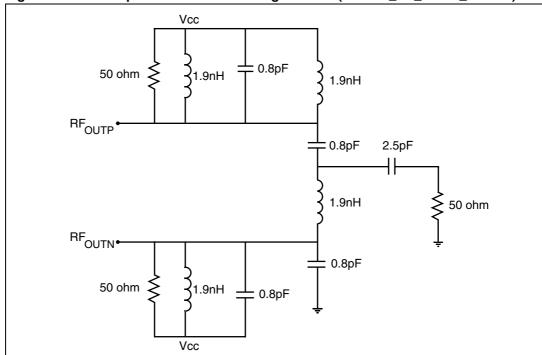

| Figure 29.               | LC lumped balun and matching network (MATCH_LC_LUMP_4G.dsn)          |      |

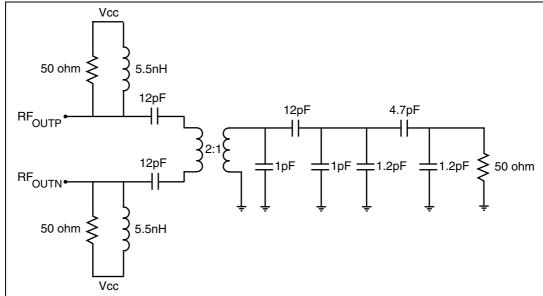

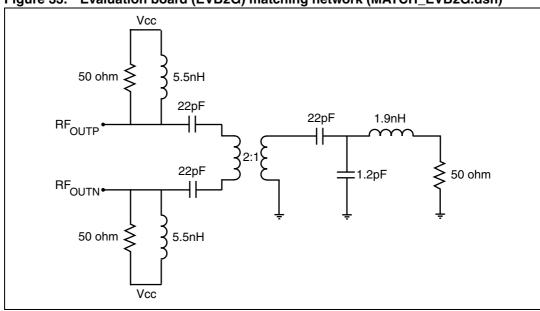

| Figure 30.               | Evaluation board (EVB4G) matching network (MATCH_EVB4G.dsn)          |      |

| Figure 31.               | Differential/single-ended output network (MATCH_LC_LUMP_2G_DIFF.dsn) |      |

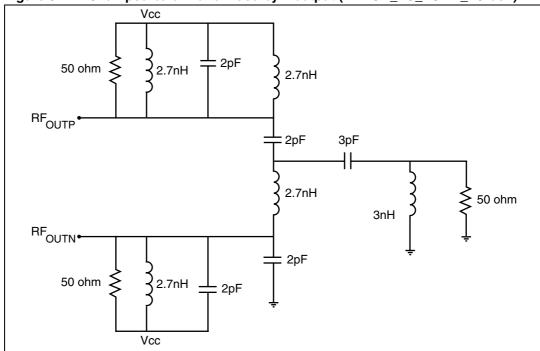

| Figure 32.               | LC lumped balun for divided by 2 output (MATCH_LC_LUMP_2G.dsn)       |      |

| Figure 33.               | Evaluation board (EVB2G) matching network (MATCH_EVB2G.dsn)          |      |

| Figure 34.               | LC lumped balun for divided by 4 output (MATCH_LC_LUMP_1G.dsn)       |      |

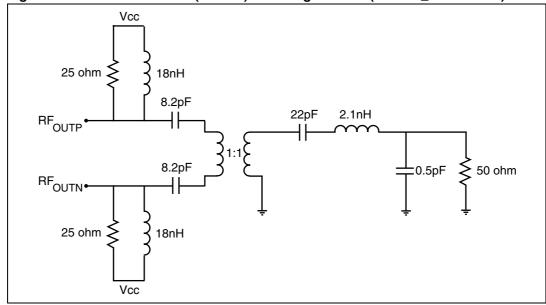

| Figure 34.<br>Figure 35. | Evaluation board (EVB1G) matching network (MATCH_EVB1G.dsn)          |      |

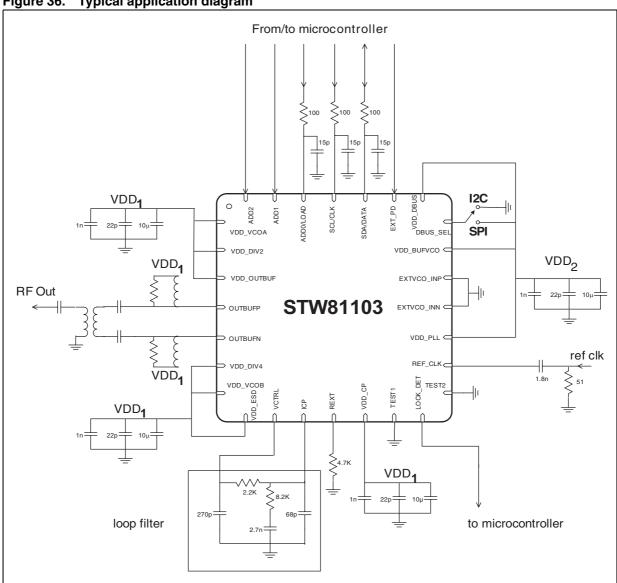

| Figure 35.<br>Figure 36. | · · · · · · · · · · · · · · · · · · ·                                |      |

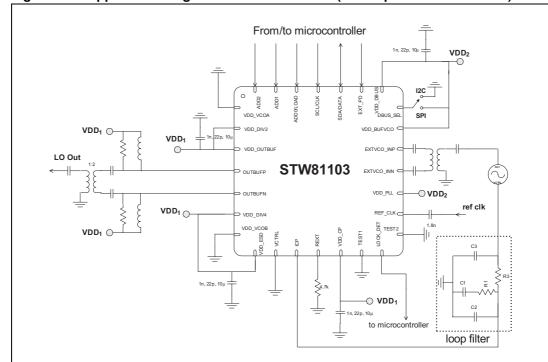

| •                        | Typical application diagram                                          |      |

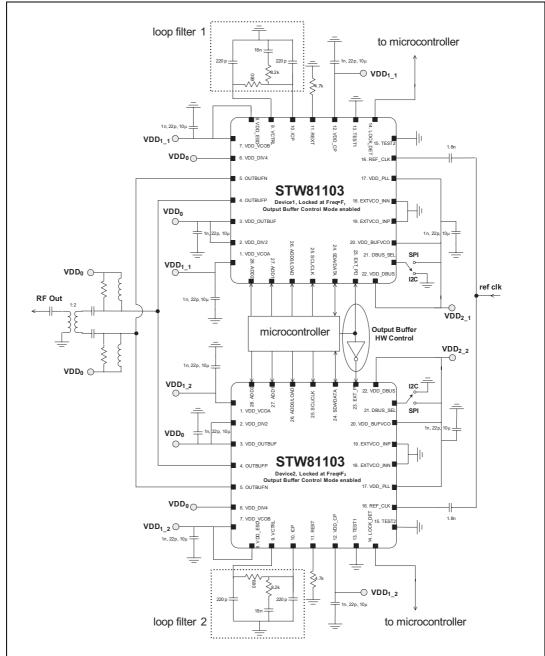

| Figure 37.               | Ping-pong architecture diagram                                       |      |

| Figure 38.               | Application diagram with external VCO (LO output from STW81103)      |      |

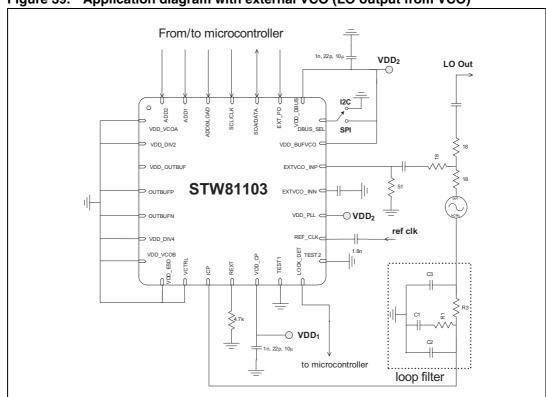

| Figure 39.               | Application diagram with external VCO (LO output from VCO)           |      |

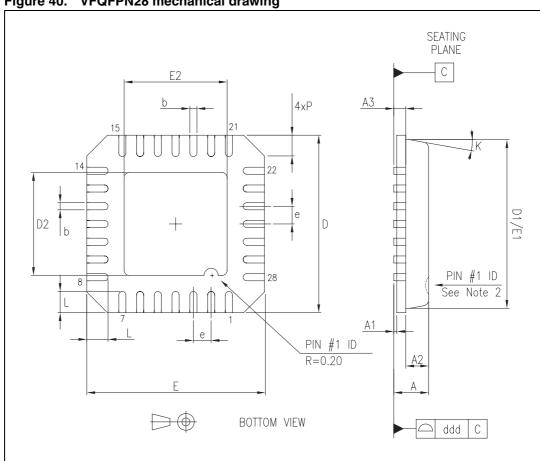

| Figure 40.               | VFQFPN28 mechanical drawing                                          | . 50 |

# 1 Block diagram and pin configuration

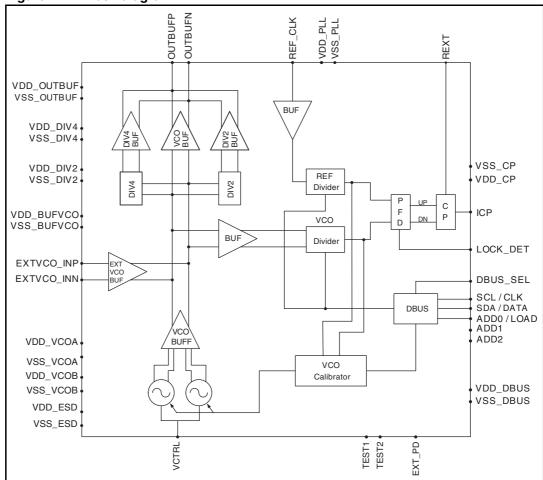

### 1.1 Block diagram

Figure 1. Block diagram

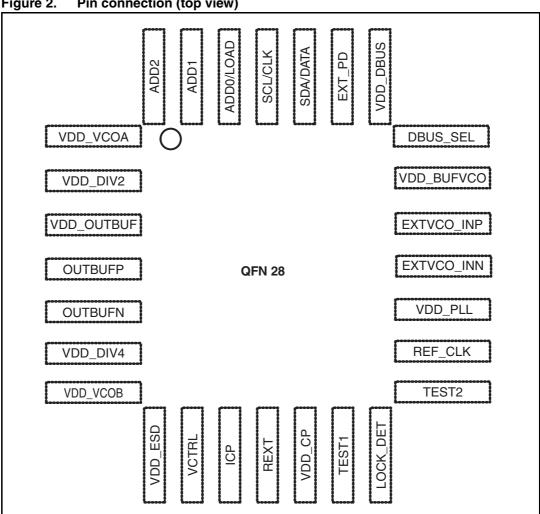

#### 1.2 Pin configuration

Figure 2. Pin connection (top view)

Table 1. Pin description

| Pin No | Name       | Description                    | Observation    |

|--------|------------|--------------------------------|----------------|

| 1      | VDD_VCOA   | VCO A power supply             |                |

| 2      | VDD_DIV2   | Divider by 2 power supply      |                |

| 3      | VDD_OUTBUF | Output buffer power supply     |                |

| 4      | OUTBUFP    | LO buffer positive output      | Open collector |

| 5      | OUTBUFN    | LO buffer negative output      | Open collector |

| 6      | VDD_DIV4   | Divider by 4 power supply      |                |

| 7      | VDD_VCOB   | VCO B power supply             |                |

| 8      | VDD_ESD    | ESD positive rail power supply |                |

| 9      | VCTRL      | VCO control voltage            |                |

Table 1. Pin description (continued)

| Pin No | Name       | Description                                        | Observation                                             |

|--------|------------|----------------------------------------------------|---------------------------------------------------------|

| 10     | ICP        | PLL charge pump output                             |                                                         |

| 11     | REXT       | External resistance connection for PLL charge pump |                                                         |

| 12     | VDD_CP     | Power supply for charge pump                       |                                                         |

| 13     | TEST1      | Test input 1                                       | For test purposes only;<br>must be connected to<br>GND  |

| 14     | LOCK_DET   | Lock detector                                      | CMOS output<br>(I <sub>OUT</sub> =4mA)                  |

| 15     | TEST2      | Test input 2                                       | For test purposes only;<br>must be connected to<br>GND  |

| 16     | REF_CLK    | Reference clock input                              |                                                         |

| 17     | VDD_PLL    | PLL digital power supply                           |                                                         |

| 18     | EXTVCO_INN | External VCO negative input                        | For test purposes only;<br>must be connected to<br>GND  |

| 19     | EXTVCO_INP | External VCO positive input                        | For test purposes only;<br>must be connected to<br>GND  |

| 20     | VDD_BUFVCO | VCO buffer power supply                            |                                                         |

| 21     | DBUS_SEL   | Digital Bus Interface select                       | CMOS input                                              |

| 22     | VDD_DBUS   | SPI and I <sup>2</sup> C bus power supply          |                                                         |

| 23     | EXT_PD     | Power down hardware '0' device ON; '1' device OFF  | CMOS input                                              |

| 24     | SDA/DATA   | I2CBUS/SPI data line                               | CMOS Bidir Schmitt<br>triggered (I <sub>OUT</sub> =4mA) |

| 25     | SCL/CLK    | I2CBUS/SPI clock line                              | CMOS input Schmitt triggered                            |

| 26     | ADD0/LOAD  | I2CBUS address select pin/ SPI load line           | CMOS input                                              |

| 27     | ADD1       | I2CBUS address select pin                          | CMOS input; must be connected to GND in SPI mode        |

| 28     | ADD2       | I2CBUS address select pin                          | CMOS input; must be connected to GND in SPI mode        |

# 2 Electrical specifications

## 2.1 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Symbol           | Parameter                                                                  | Values          | Unit |

|------------------|----------------------------------------------------------------------------|-----------------|------|

| $AV_{CC}$        | Analog supply voltage                                                      | 0 to 4.6        | V    |

| DV <sub>CC</sub> | Digital supply voltage                                                     | 0 to 4.6        | V    |

| T <sub>stg</sub> | Storage temperature                                                        | +150            | °C   |

| ESD              | Electrical static discharge - HBM <sup>(1)</sup> - CDM-JEDEC standard - MM | 4<br>1.5<br>0.2 | kV   |

<sup>1.</sup> The maximum rating of the ESD protection circuitry on pin 4 and pin 5 is 800 V.

## 2.2 Operating conditions

Table 3. Operating conditions (1)

| Symbol              | Parameter                                      | Test conditions        | Min. | Тур. | Max. | Units |

|---------------------|------------------------------------------------|------------------------|------|------|------|-------|

| AV <sub>CC</sub>    | Analog supply voltage                          |                        | 3.0  | 3.3  | 3.6  | V     |

| DV <sub>CC</sub>    | Digital supply voltage                         |                        | 3.0  | 3.3  | 3.6  | V     |

| I <sub>VDD1</sub>   | V <sub>DD1</sub> current consumption           |                        |      | 90   |      | mA    |

| I <sub>VDD2</sub>   | V <sub>DD2</sub> current consumption           |                        |      | 12   |      | mA    |

| T <sub>amb</sub>    | Operating ambient temperature                  |                        | -40  |      | 85   | °C    |

| Tj                  | Maximum junction temperature                   |                        |      |      | 125  | °C    |

| R <sub>th j-a</sub> | Junction to ambient package thermal resistance | Multilayer JEDEC board |      | 44   |      | °C/W  |

| R <sub>th j-b</sub> | Junction to board package thermal resistance   | Multilayer JEDEC board |      | 26.3 |      | °C/W  |

| R <sub>th j-c</sub> | Junction to case package thermal resistance    | Multilayer JEDEC board |      | 6.3  |      | °C/W  |

<sup>1.</sup> Refer to Figure 36: Typical application diagram.

# 2.3 Digital logic levels

Table 4. Digital logic levels

| Symbol            | Parameter                  | Test conditions | Min.     | Тур. | Max.    | Units |

|-------------------|----------------------------|-----------------|----------|------|---------|-------|

| V <sub>il</sub>   | Low-level input voltage    |                 |          |      | 0.2*Vdd | V     |

| V <sub>ih</sub>   | High-level input voltage   |                 | 0.8*Vdd  |      |         | V     |

| V <sub>hyst</sub> | Schmitt trigger hysteresis |                 | 0.8      |      |         | V     |

| V <sub>ol</sub>   | Low-level output voltage   |                 |          |      | 0.4     | V     |

| V <sub>oh</sub>   | High-level output voltage  |                 | 0.85*Vdd |      |         | V     |

## 2.4 Electrical specifications

All electrical specifications are intended for a 3.3 V supply voltage.

Table 5. Electrical specifications

| Symbol            | Parameter                                  | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Min.                        | Тур. | Max.                      | Unit  |

|-------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|---------------------------|-------|

| Output fre        | quency range                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |      |                           |       |

|                   |                                            | Direct output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2500                        |      | 3050                      | MHz   |

| F <sub>OUTA</sub> | Output frequency range with VCOA           | Divider by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1250                        |      | 1525                      | MHz   |

|                   |                                            | Direct output   2500   3050   3050   255   255   2500   255   2500   255   2500   255   2500   255   2500   255   2500   2500   255   2500   255   2500   255   2500   255   2500   255   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   2550   255 | MHz                         |      |                           |       |

|                   |                                            | Direct output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4350                        |      | 5000                      | MHz   |

| F <sub>OUTB</sub> | Output frequency range with VCOB           | Divider by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2175                        |      | 2500                      | MHz   |

|                   | VCOB                                       | Divider by 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1087.5                      |      | 1250                      | MHz   |

| VCO divide        | ers                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |      |                           |       |

| N.                | VCO divider ratio                          | Prescaler 16/17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 256                         |      | 65551                     |       |

| N                 |                                            | Prescaler 19/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 361                         |      | 77836                     |       |

| Reference         | clock and phase frequency d                | etector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             |      |                           |       |

| F <sub>ref</sub>  | Reference input frequency                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10                          |      | 200                       | MHz   |

|                   | Reference input sensitivity <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.35                        | 1    | 1.5                       | Vpeak |

| R                 | Reference divider ratio                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                           |      | 1023                      |       |

| F <sub>PFD</sub>  | PFD input frequency                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |      | 16                        | MHz   |

| E.                | Fraguanay stan <sup>(2)</sup>              | Prescaler 16/17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |      | F <sub>OUT</sub> /<br>256 | Hz    |

| F <sub>STEP</sub> | Trieducticy steh.                          | Prescaler 19/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | F <sub>OUT</sub> /<br>77836 |      | F <sub>OUT</sub> /<br>361 | Hz    |

10/53

Table 5. Electrical specifications (continued)

| Symbol              | Electrical specifications  Parameter             | Condition                                 | Min. | Тур. | Max.                 | Unit  |

|---------------------|--------------------------------------------------|-------------------------------------------|------|------|----------------------|-------|

| Charge pu           | ımp                                              |                                           |      | 1    |                      |       |

| I <sub>CP</sub>     | ICP sink/source <sup>(3)</sup>                   | 3-bit programmable                        |      |      | 5                    | mA    |

| V <sub>OCP</sub>    | Output voltage compliance range                  |                                           | 0.4  |      | V <sub>dd</sub> -0.3 | V     |

|                     |                                                  | Direct output (F <sub>PFD</sub> =200 kHz) |      | -76  |                      | dBc   |

|                     | Spurious <sup>(4)</sup>                          | Divider by 2 (F <sub>PFD</sub> =400 kHz)  |      | -82  |                      | dBc   |

|                     |                                                  | Divider by 4 (F <sub>PFD</sub> =800 kHz)  |      | -88  |                      | dBc   |

| VCOs                |                                                  |                                           |      |      |                      |       |

|                     |                                                  | Lower frequency range                     | 45   | 65   | 85                   | MHz/V |

| K <sub>VCOA</sub>   | VCOA sensitivity <sup>(5)</sup>                  | Intermediate frequency range              | 60   | 80   | 105                  | MHz/V |

|                     |                                                  | Higher frequency range                    | 85   | 105  | 145                  | MHz/V |

|                     |                                                  | Lower frequency range                     | 45   | 65   | 85                   | MHz/V |

| K <sub>VCOB</sub>   | VCOB sensitivity <sup>(5)</sup>                  | Intermediate frequency range              | 60   | 80   | 100                  | MHz/V |

|                     |                                                  | Higher frequency range                    | 85   | 100  | 130                  | MHz/V |

|                     | Maximum temperature                              | VCO A                                     | 125  |      |                      | °C    |

| $\Delta T_{LK}$     | variation for continuous lock <sup>(5) (6)</sup> | VCO B                                     | 95   |      |                      | °C    |

|                     | VCOA pushing <sup>(5)</sup>                      |                                           |      | 4    | 7                    | MHz/V |

|                     | VCOB pushing <sup>(5)</sup>                      |                                           |      | 15   | 21                   | MHz/V |

| V <sub>CTRL</sub>   | VCO control voltage <sup>(5)</sup>               |                                           | 0.4  |      | 3                    | V     |

|                     | LO harmonic spurious <sup>(5)</sup>              |                                           |      |      | -20                  | dBc   |

| l                   | VCOA current consumption                         | F <sub>VCO</sub> =2.8 GHz; amplitude[11]  |      | 30   |                      | mA    |

| I <sub>VCOA</sub>   | VCOA current consumption                         | F <sub>VCO</sub> =2.8 GHz; amplitude[00]  |      | 16   |                      | mA    |

| lugge               | VCOB current consumption                         | F <sub>VCO</sub> =4.7 GHz; amplitude[11]  |      | 24   |                      | mA    |

| I <sub>VCOB</sub>   | VOOD current consumption                         | F <sub>VCO</sub> =4.7 GHz; amplitude[00]  |      | 13   |                      | mA    |

| I <sub>VCOBUF</sub> | VCO buffer consumption                           |                                           |      | 15   |                      | mA    |

| $I_{DIV2}$          | Divider by 2 consumption                         |                                           |      | 17   |                      | mA    |

| I <sub>DIV4</sub>   | Divider by 4 consumption                         |                                           |      | 14   |                      | mA    |

| LO output           | buffer                                           |                                           |      |      |                      |       |

| $P_{LO}$            | Output level                                     |                                           |      | 0    |                      | dBm   |

| $R_{L}$             | Return loss                                      | Matched to 50 ohms                        |      | 15   |                      | dB    |

|                     |                                                  | DIV4 Buff                                 |      | 26   |                      | mA    |

| I <sub>OUTBUF</sub> | Current consumption                              | DIV2 Buff                                 |      | 23   |                      | mA    |

|                     |                                                  | Direct output                             |      | 39   |                      | mA    |

Table 5. **Electrical specifications (continued)**

| Symbol            | Parameter                      | Condition                                           | Min.  | Тур. | Max. | Unit |  |  |

|-------------------|--------------------------------|-----------------------------------------------------|-------|------|------|------|--|--|

| External VCO      |                                |                                                     |       |      |      |      |  |  |

|                   | Frequency range                |                                                     | 0.625 |      | 5.0  | GHz  |  |  |

|                   | Input level                    |                                                     | -10   |      | +6   | dBm  |  |  |

|                   | Current consumption            | VCO internal buffer                                 |       | 28   |      | mA   |  |  |

| PLL misce         | PLL miscellaneous              |                                                     |       |      |      |      |  |  |

| I <sub>PLL</sub>  | Current consumption            | Input buffer, prescaler, digital dividers, misc.    |       | 12   |      | mA   |  |  |

| t <sub>lock</sub> | Lockup time <sup>(5) (7)</sup> | 25 kHzPLLbandwidth; within 1 ppm of frequency error |       | 150  |      | μs   |  |  |

- 1. In order to achieve best phase noise performance 1 V peak level is suggested.

- 2. The frequency step is related to the PFD input frequency as follows:

- F<sub>step</sub> = F<sub>PFD</sub> for direct output F<sub>step</sub> = F<sub>PFD</sub>/2 for divided by 2 output F<sub>step</sub> = F<sub>PFD</sub>/4 for divided by 4 output

- 3. See relationship between ICP and REXT in Section 5.7: Charge pump.

- 4. The level of the spurs may change depending on PFD frequency, charge pump current, selected channel and PLL loop

- 5. Guaranteed by design and specification.

- When setting a specified output frequency, the VCO calibration procedure must be run in order to select the best sub-range when setting a specified output frequency, the VCO calibration procedure fruits be full in order to select the best sub-range for the VCO covering the desired frequency. Once programmed at the initial temperature  $T_0$  inside the operating temperature range (-40 °C to +85 °C), the synthesizer is able to maintain the lock status only if the temperature drift (in either direction) is within the limit specified by  $\Delta T_{LK}$ , provided that the final temperature  $T_1$  is still inside the nominal range. If higher  $\Delta T$  are required the "VCO calibration auto-restart" feature can be enabled, thus allowing to re-start the VCO calibration procedure automatically when the part loose the lock condition (trigger on lock detector signal).

- 7. Frequency jump from 2250 to 2400 MHz; it includes the time required by the VCO calibration procedure (7  $F_{PFD}$  cycles with  $F_{PFD}$ =400 kHz).

# 2.5 Phase noise specification

Table 6. Phase noise specification <sup>(1)</sup>

| Parameter                              | Test conditions                                                                         | Min.    | Тур.         | Max.                 | Unit   |

|----------------------------------------|-----------------------------------------------------------------------------------------|---------|--------------|----------------------|--------|

| In-band phase noise floor - clo        | sed loop <sup>(2)</sup>                                                                 |         |              |                      |        |

| Normalized inband phase noise floor    |                                                                                         |         | -222         |                      | dBc/Hz |

| Inband phase noise floor direct output | ICP=4 mA, PLL BW=50 kHz;                                                                | -222+20 | Dlog(N)+10lo | g(F <sub>PFD</sub> ) | dBc/Hz |

| Inband phase noise floor divider by 2  | including reference clock contribution                                                  | -228+20 | Dlog(N)+10lo | g(F <sub>PFD</sub> ) | dBc/Hz |

| Inband phase noise floor divider by 4  |                                                                                         | -234+20 | Dlog(N)+10lo | g(F <sub>PFD</sub> ) | dBc/Hz |

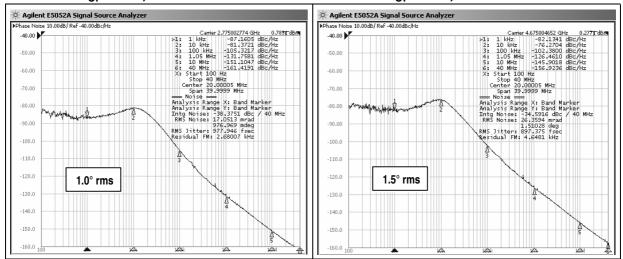

| PLL integrated phase noise – d         | irect output                                                                            |         |              |                      |        |

| Integrated phase noise                 | F <sub>OUT</sub> =4.675 GHz,<br>F <sub>PFD</sub> =200 kHz, F <sub>STEP</sub> =200 kHz,  |         | -34.6        |                      | dBc    |

| 100 Hz to 40 MHz                       | PLL BW = 15 kHz, ICP=3 mA                                                               |         | 1.5          |                      | ° rms  |

| PLL integrated phase noise – d         | ivider by 2                                                                             |         |              |                      |        |

| Integrated phase noise                 | F <sub>OUT</sub> =2.3376 GHz,<br>F <sub>PFD</sub> =400 kHz, F <sub>STEP</sub> =200 kHz, |         | -42.6        |                      | dBc    |

| 100 Hz to 40 MHz                       | PLL BW=25 kHz, ICP=2 mA                                                                 |         | 0.6          |                      | ° rms  |

| PLL integrated phase noise – d         | ivider by 4                                                                             | I.      | ·            |                      | I.     |

| Integrated phase noise                 | F <sub>OUT</sub> =1.1688 GHz,<br>F <sub>PFD</sub> =800 kHz, F <sub>STEP</sub> =200 kHz, |         | -49.5        |                      | dBc    |

| 100 Hz to 40 MHz                       | PLL BW=35 kHz, ICP=1.5 mA                                                               |         | 0.27         |                      | ° rms  |

| VCO A direct (2500 MHz-3050 N          | IHz) – open loop <sup>(3)</sup>                                                         | I       | L            |                      | I      |

| Phase noise @ 1 kHz                    |                                                                                         |         | -59          |                      | dBc/Hz |

| Phase noise @ 10 kHz                   |                                                                                         |         | -87          |                      | dBc/Hz |

| Phase noise @ 100 kHz                  |                                                                                         |         | -109         |                      | dBc/Hz |

| Phase noise @ 1 MHz                    |                                                                                         |         | -131         |                      | dBc/Hz |

| Phase noise @ 10 MHz                   |                                                                                         |         | -151         |                      | dBc/Hz |

| Phase noise @ 40 MHz                   |                                                                                         |         | -161         |                      | dBc/Hz |

| VCO B direct (4350 MHz-5000 M          | IHz) – open loop <sup>(3)</sup>                                                         | l .     | ·            |                      | l .    |

| Phase noise @ 1 kHz                    |                                                                                         |         | -54          |                      | dBc/Hz |

| Phase noise @ 10 kHz                   |                                                                                         |         | -82          |                      | dBc/Hz |

| Phase noise @ 100 kHz                  |                                                                                         |         | -105         |                      | dBc/Hz |

| Phase noise @ 1 MHz                    |                                                                                         |         | -127         |                      | dBc/Hz |

| Phase noise @ 10 MHz                   |                                                                                         |         | -147         |                      | dBc/Hz |

| Phase noise @ 40 MHz                   |                                                                                         |         | -157         |                      | dBc/Hz |

Table 6. Phase noise specification (1) (continued)

| Parameter                          | Test conditions                        | Min.     | Тур. | Max. | Unit   |

|------------------------------------|----------------------------------------|----------|------|------|--------|

| VCO A with divider by 2 (1250 MHz- | 1525 MHz) – open loop <sup>(3)</sup>   | <u> </u> |      | ·    |        |

| Phase noise @ 1 kHz                |                                        |          | -65  |      | dBc/Hz |

| Phase noise @ 10 kHz               |                                        |          | -93  |      | dBc/Hz |